Prima dei microprocessori (1) - Vintage

computer technologies (before micros - 1)

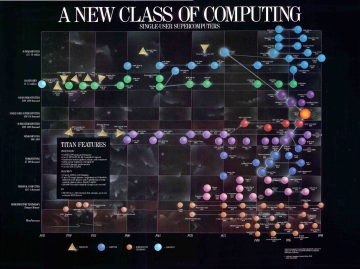

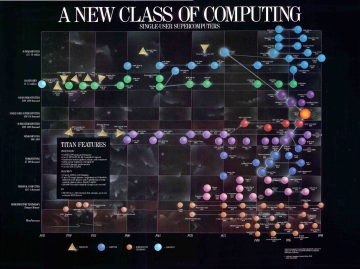

Questa

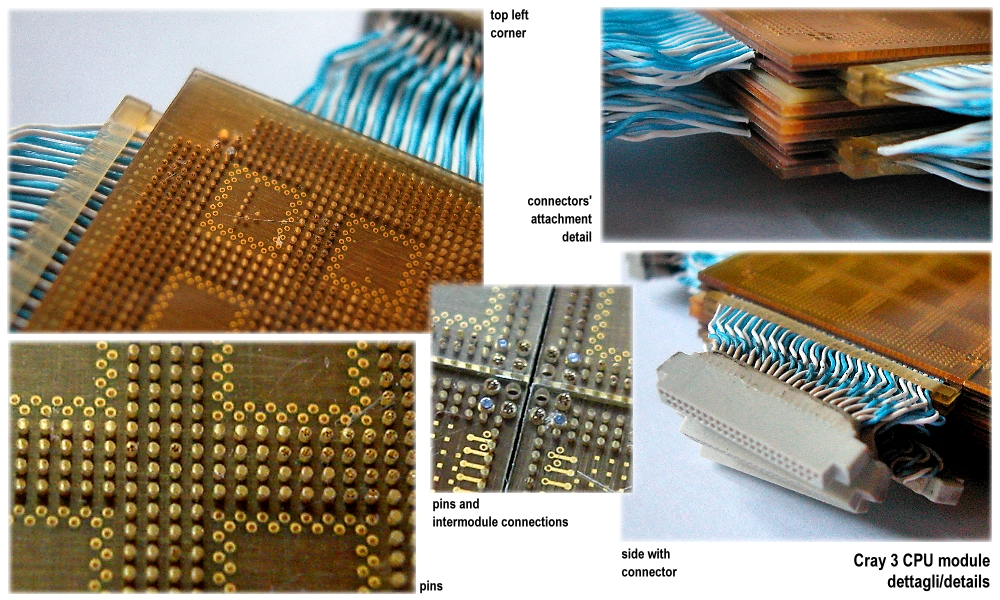

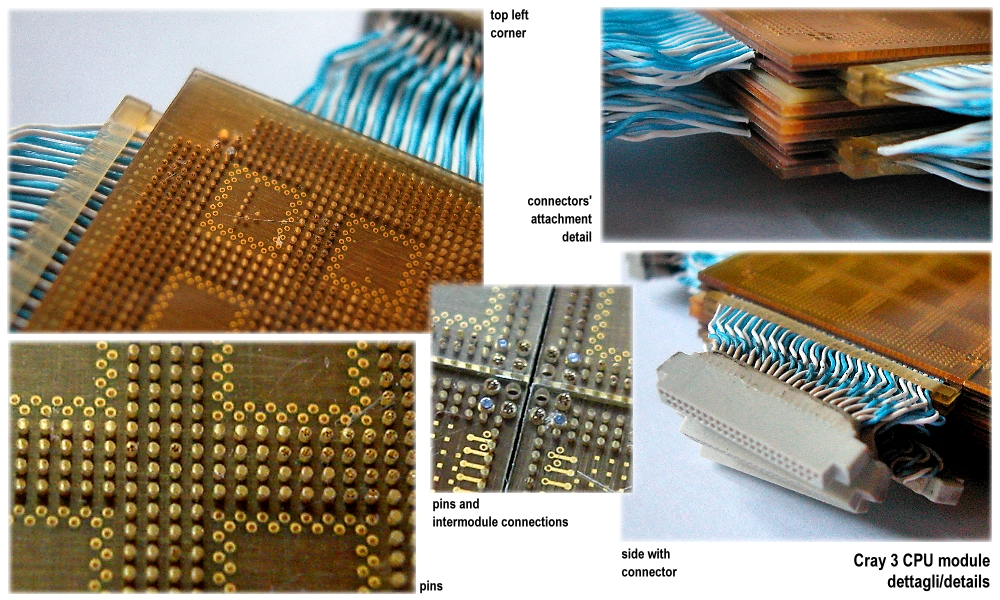

immagine (scarica la

versione JPEG ad alta risoluzione, circa 650 KB) riproduce un poster del

1988 che raffigura lo sviluppo delle tecnologie di realizzazione dei calcolatori

elettronici nel periodo 1946-1986 circa (vedi).

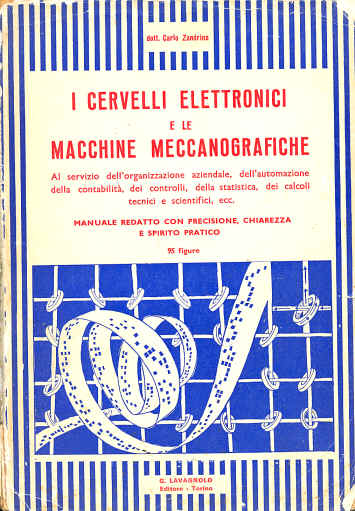

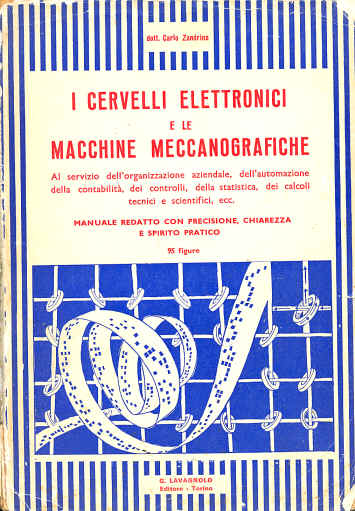

Il libro

"I cervelli elettronici e le macchine meccanografiche" di C.

Zandrino (Lavagnolo, 1961) è stato uno dei primissimi testi pubblicati in

Italia che abbiano trattato estesamente, dal punto di vista delle applicazioni e

dei possibili utilizzatori e non solamente a livello teorico, l'argomento

"calcolatori elettronici", all'epoca visto ancora con timoroso

rispetto da parte di molti. All'inizio degli anni Sessanta l'informatica nel

nostro Paese muoveva i primi passi: i pochi elaboratori esistenti, in massima

parte IBM, erano di proprietà di banche, compagnie di assicurazione ed Enti

pubblici (ad esempio l'INPS). Non erano invece ancora penetrati nel settore

industriale, con poche eccezioni significative tra cui FIAT, Pirelli e

Montedison. L'autore si rivolge ad un pubblico appunto "aziendale" di

manager ed imprenditori, cercando di mettere in luce pregi e difetti dei

principali calcolatori elettronici disponibili sul mercato e ponendo sempre

l'accento sulle loro applicazioni pratiche. Non manca qualche ingenuità, come

ad esempio quando nella descrizione dell'IBM 7090, un calcolatore a transistor

derivato dal precedente modello 709 ed esplicitamente progettato per eseguire

complesse applicazioni scientifiche, egli scrive che questa macchina "trova

applicazione nei calcoli ingegneristici così come nella contabilità e nelle

paghe". Dubito che mai un 7090 abbia elaborato paghe od inventari! Il libro

era comunque molto aggiornato, dal momento che il 7090 era stato presentato solo

pochi mesi prima (Dicembre 1960). Le "macchine meccanografiche",

termine oggi sconosciuto ai più, anche note come "macchine

elettroncontabili", erano macchine elettromeccaniche scriventi progettate

per compiere in modo semiautomatico alcune tipiche applicazioni d'ufficio, come

ad esempio la tenuta della contabilità in partita doppia e dell'inventario, la

redazione delle fatture di vendita e così via. Sono del tutto scomparse durante

gli anni Settanta con l'avvento dei primi minicomputer per uso commerciale (per

dare un'occhiata a questo variegato mondo ormai dimenticato: http://www.ntasrl.com/upload/documenti/Frammenti%20di%20vita%209.pdf).

Vedi

(interessante): http://www.edixxon.com/computerstory/immagini/pgn_1069_000.html.

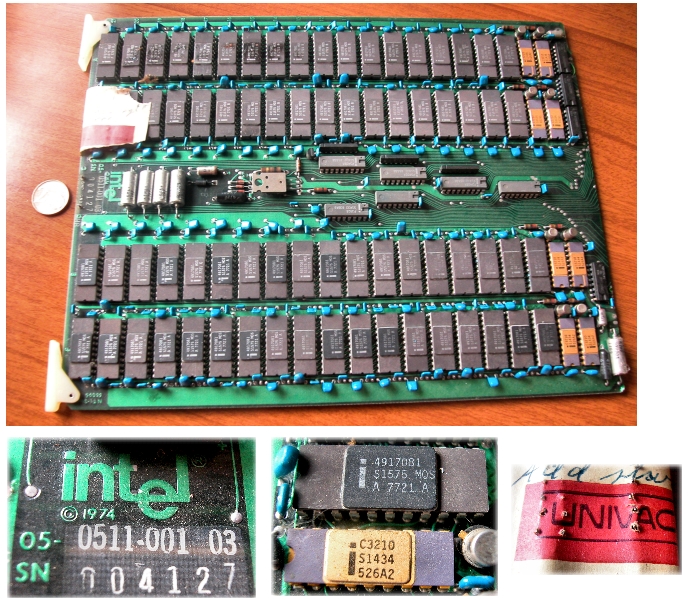

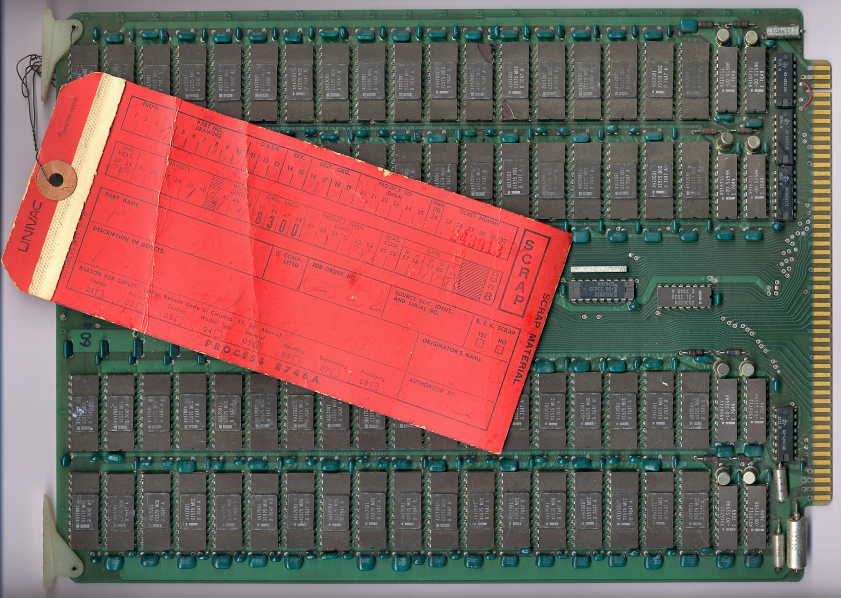

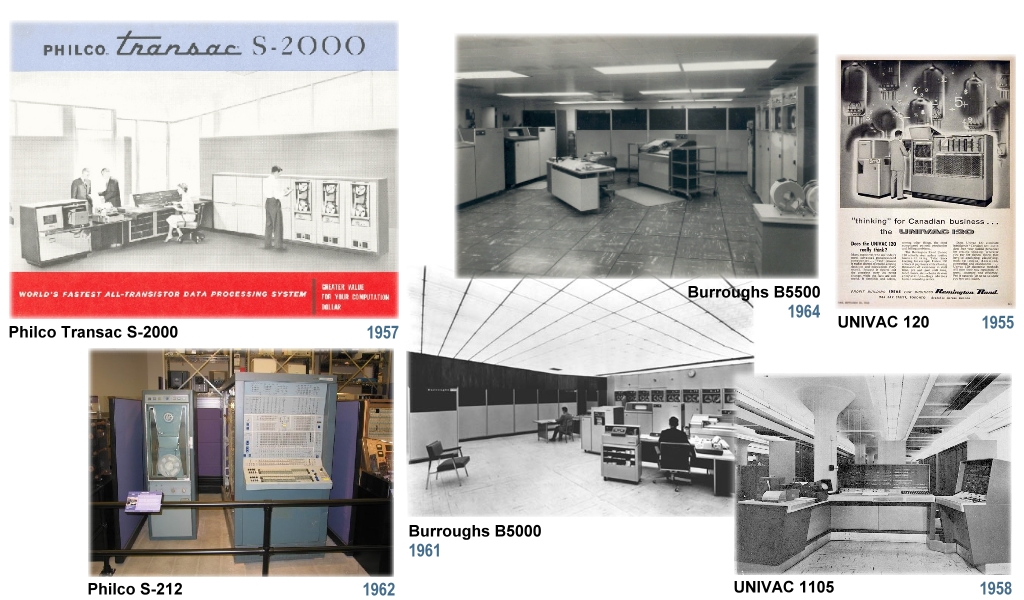

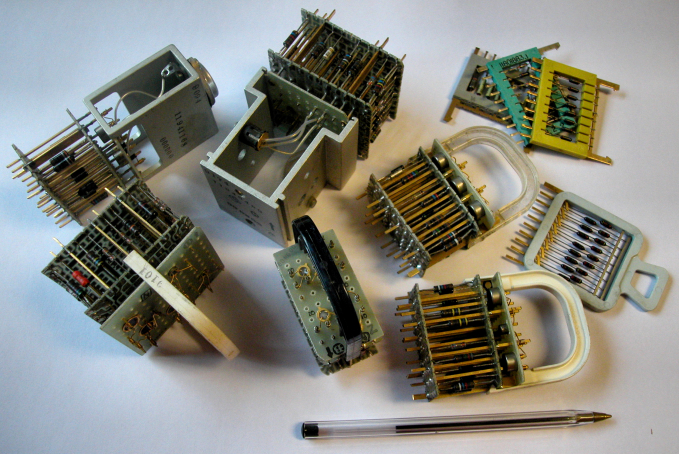

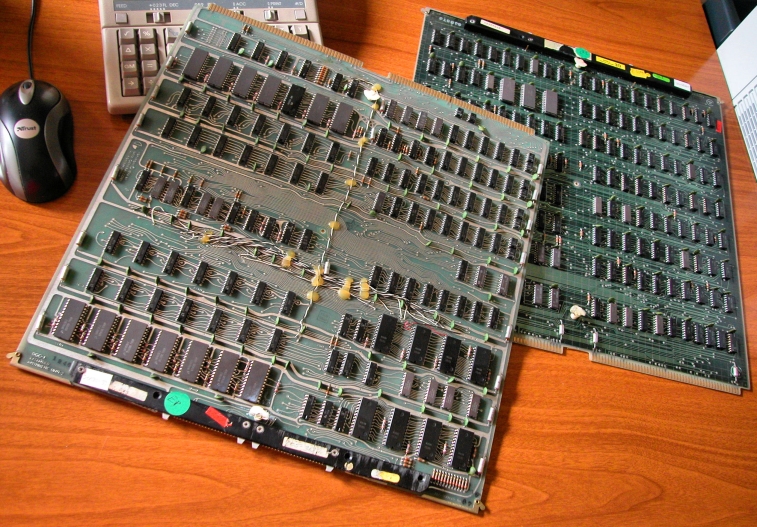

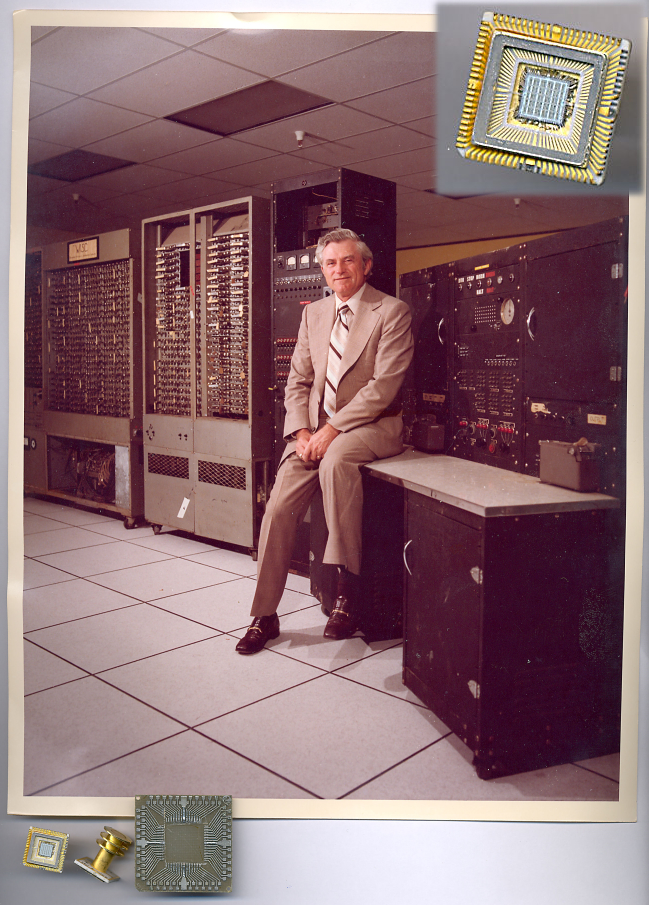

Alcune

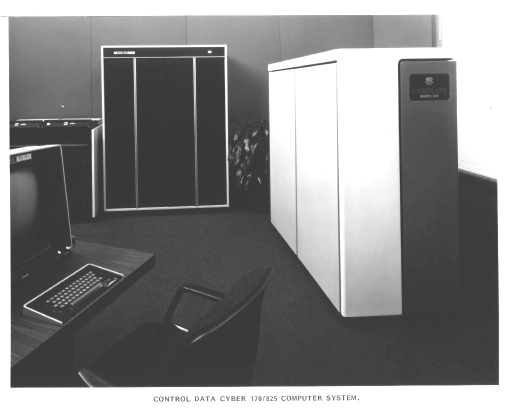

delle macchine cui appartenevano i componenti mostrati qui di seguito.

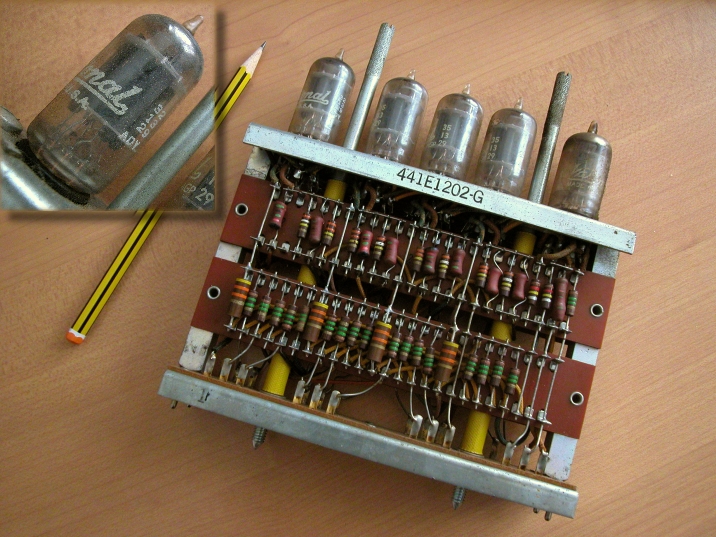

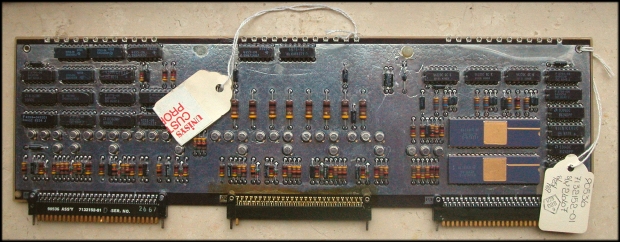

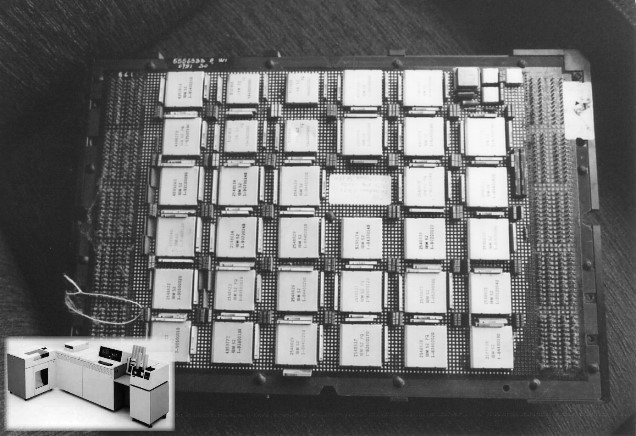

Questa

immagine raffigura un modulo plug-in a valvole fabbricato nel 1958 ed

appartenuto, forse, ad un calcolatore UNIVAC - probabilmente un UNIVAC II

oppure un più piccolo UNIVAC-120, considerato l’anno di fabbricazione. Contiene cinque doppi triodi "computer-grade"

National 5963. Benché il produttore non sia identificabile con certezza (chi

l’ha venduta su Ebay afferma che la scheda proviene da un lotto di materiali

UNIVAC) questo modulo raffigura con efficacia la tecnologia impiegata nei

calcolatori elettronici della cosiddetta "prima generazione".

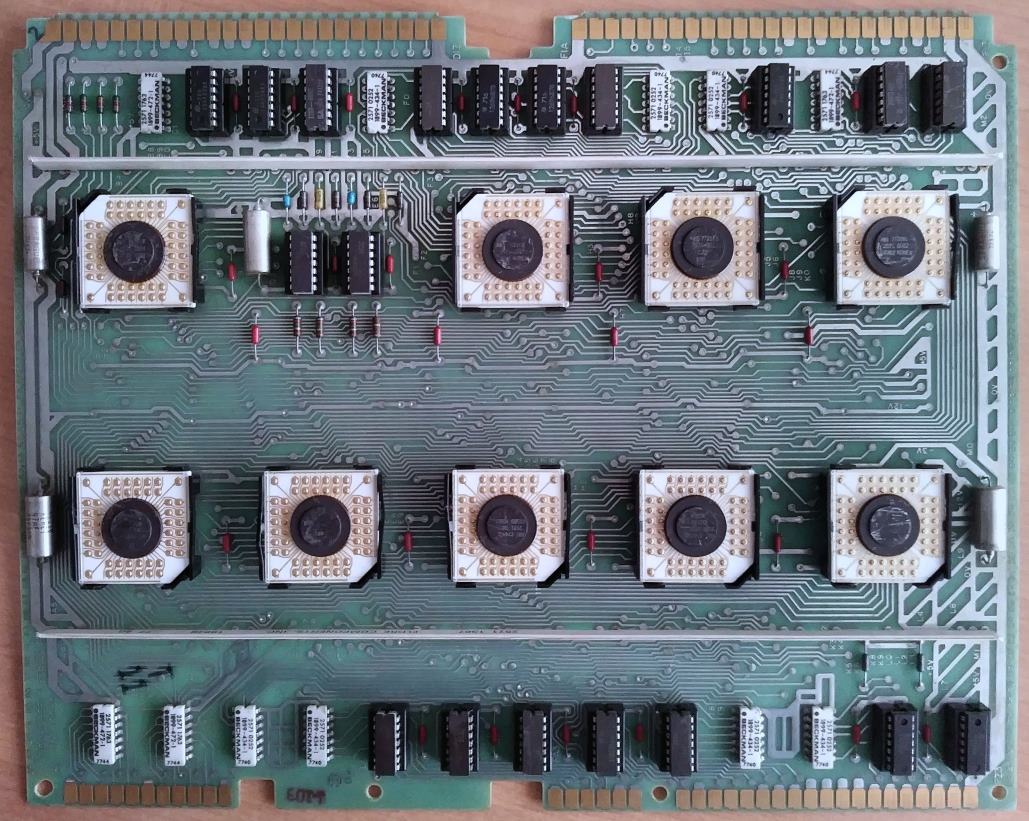

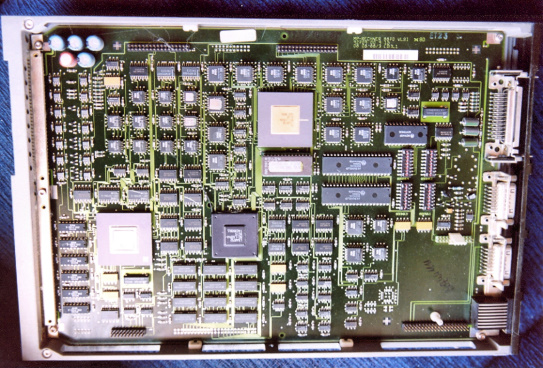

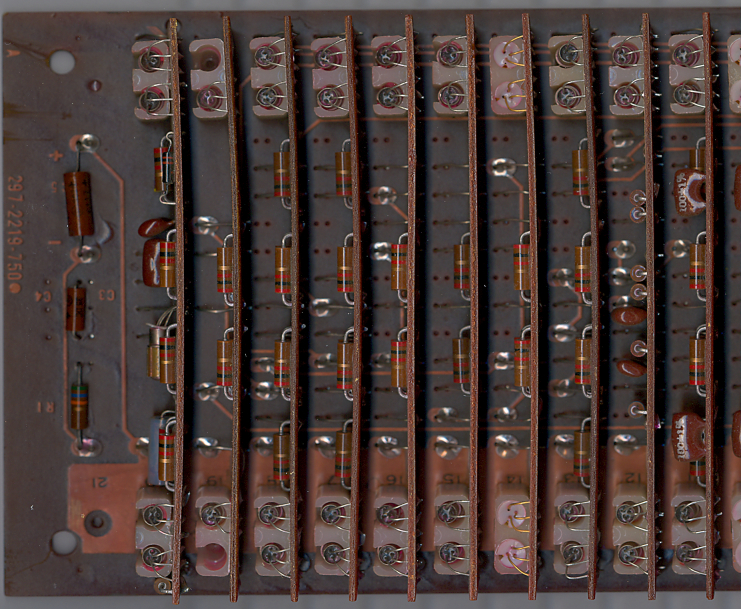

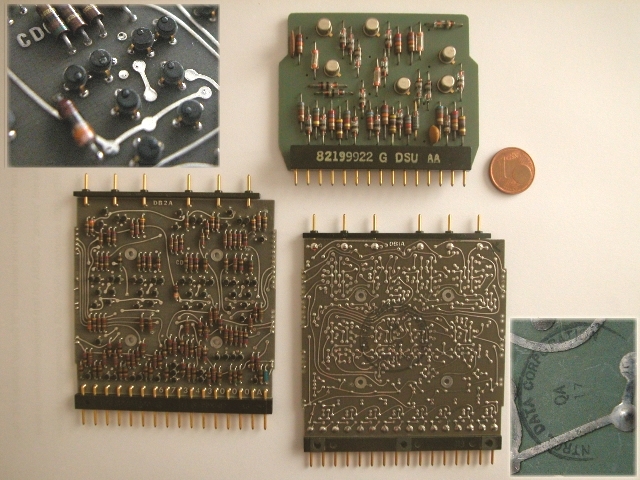

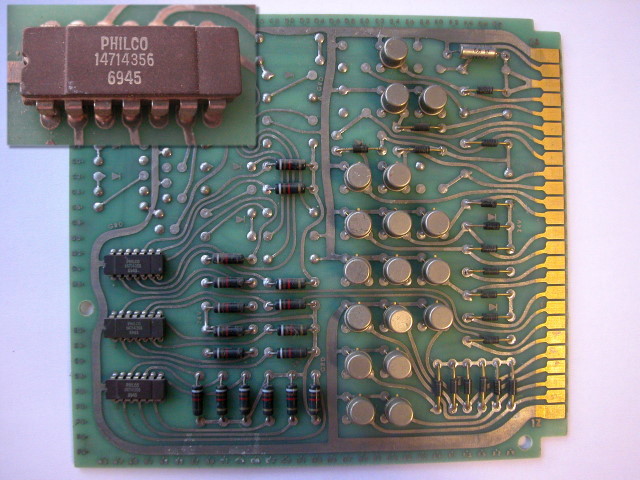

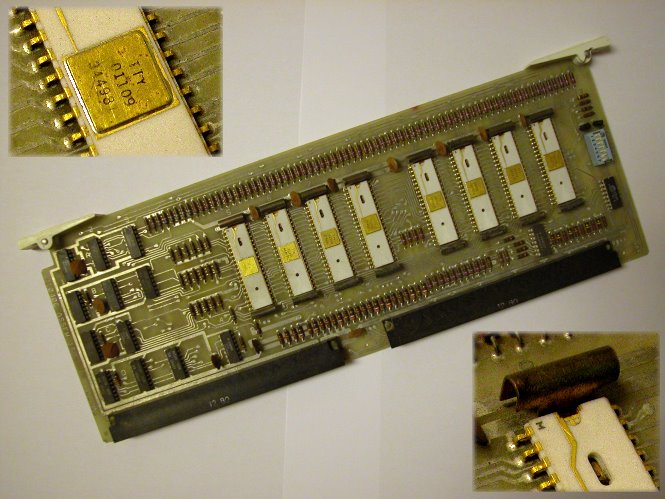

Una

delle schede della CPU di un calcolatore Philco Transac S-2000 (1957).

Questa macchina è stata, assieme all'IBM

608, il primo calcolatore elettronico commerciale

interamente a transistor. Gli ingegneri della Philco inventarono nel 1954 il Surface

Barrier Transistor (SBT),

il primo modello di transistor sufficientemente rapido (in termini di tempo di

commutazione) per essere impiegato in circuiti digitali veloci. L'S-2000 deriva

dal precedente modello S-1000 "SOLO", una rielaborazione a transistor

dell'architettura dell'Univac 1103, prodotto in pochi esemplari per la Marina

degli Stati Uniti. I transistor SBT vennero utilizzati anche in altri

calcolatori elettronici degli anni Cinquanta, come il TX-0

del 1956 (primo calcolatore elettronico a transistor, sviluppato ai Lincoln

Laboratories del MIT) e l'Univac

LARC. L'S-2000 era un calcolatore progettato per usi scientifici, ispirato

alla Macchina IAS, con

architettura a 48 bit e virgola mobile a 36+12 bit; la memoria RAM centrale, a

nuclei magnetici, era ampia 4 KB (espandibili a 64) con un tempo di accesso di

circa 10 microsecondi. Il Transac S-2000 è anche conosciuto come "Philco

210". Philco rimase

attiva nel settore dei calcolatori elettronici fino al 1965.

"In 1954, engineers at Philco Corporation invented the surface barrier transistor, the first transistor suitable for use in high-speed computers. Philco set up a computer activity - eventually a computer division - and in 1957 introduced the

Philco Transac S-2000, the first large-scale, transistorized scientific computer system offered as a product by a computer manufacturer. In the spring of 1958, we were hired by Philco to organize a programming systems department to provide software support for the new computer system. We present part of the history of the Philco computer effort from one participant's point of view. Despite a number of successful installations, the Philco computer division lacked adequate resources to remain competitive in an area dominated by IBM, and Philco withdrew from the general-purpose computer field in 1965"

(IEEE Annals of the History of Computing, vol. 26 issue 2, April-June

2004)

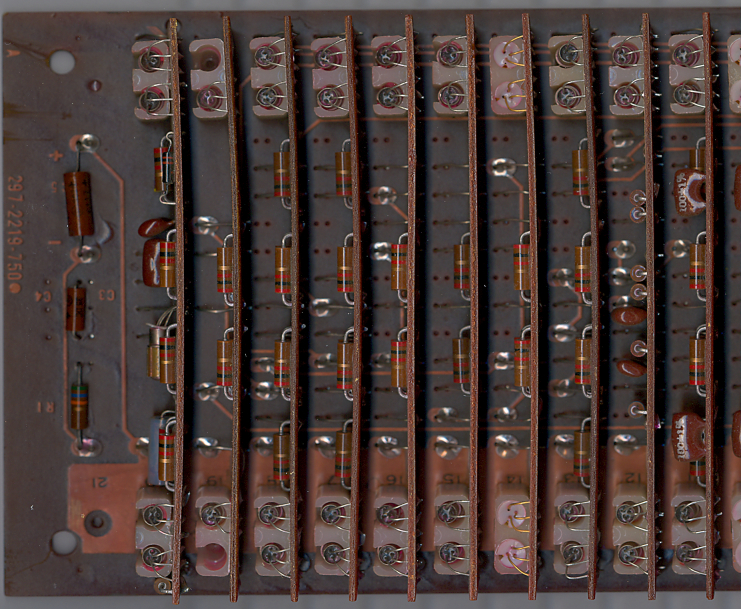

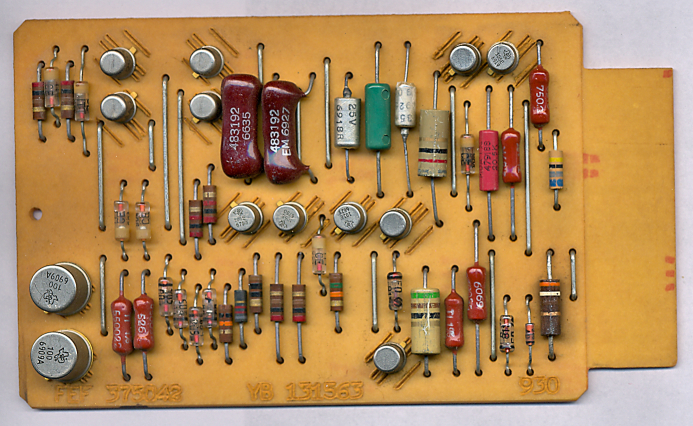

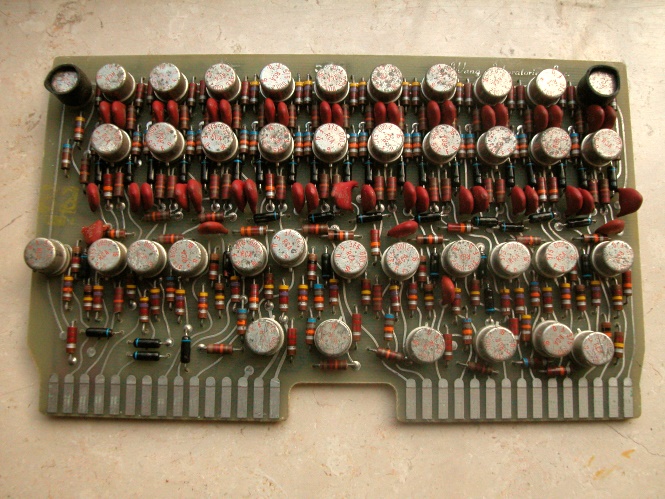

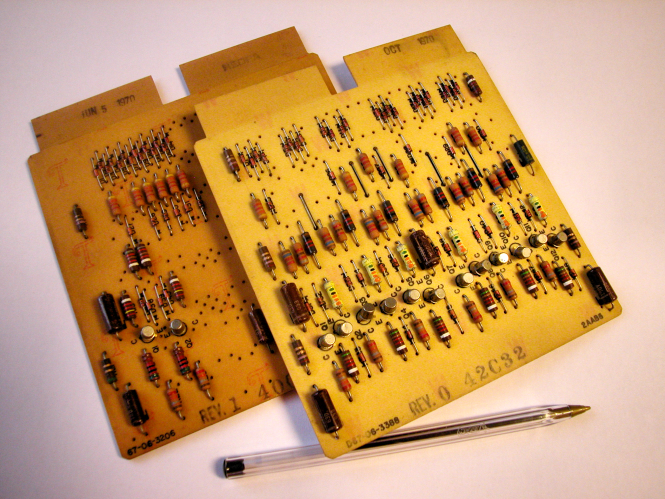

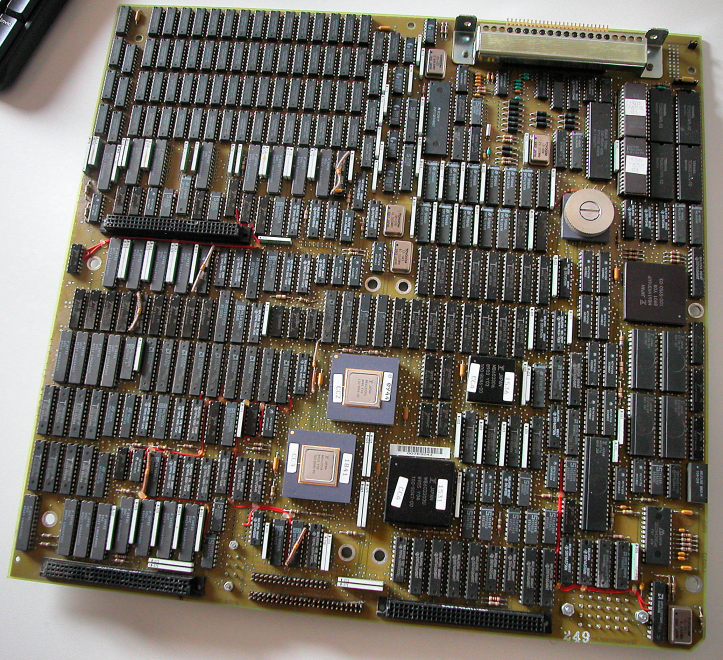

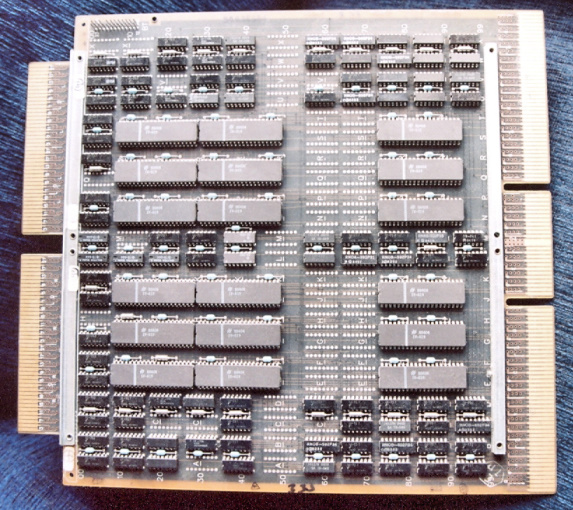

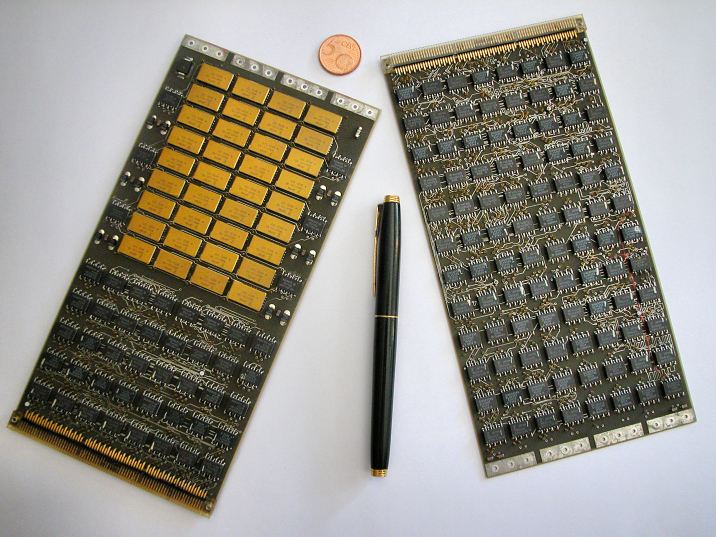

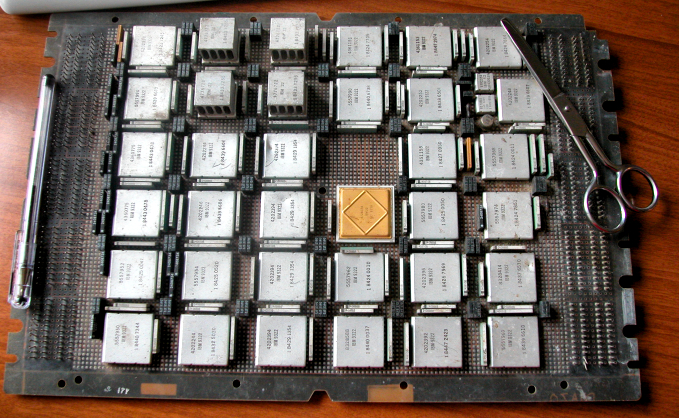

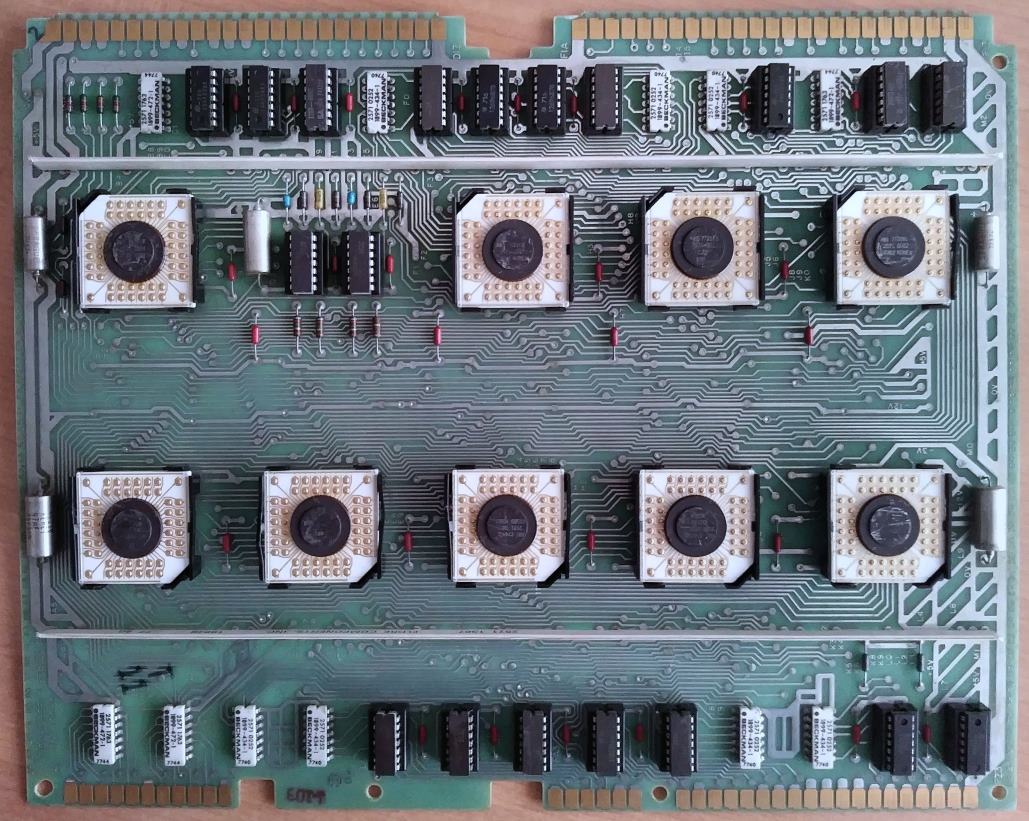

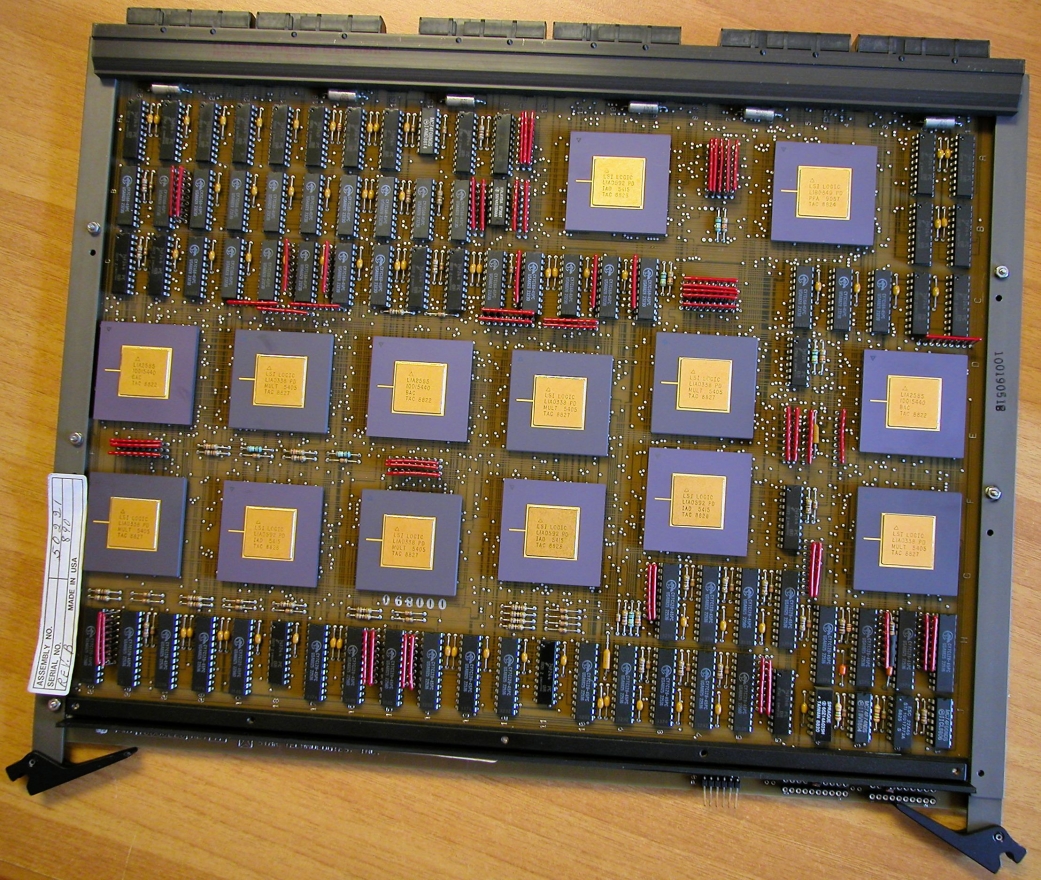

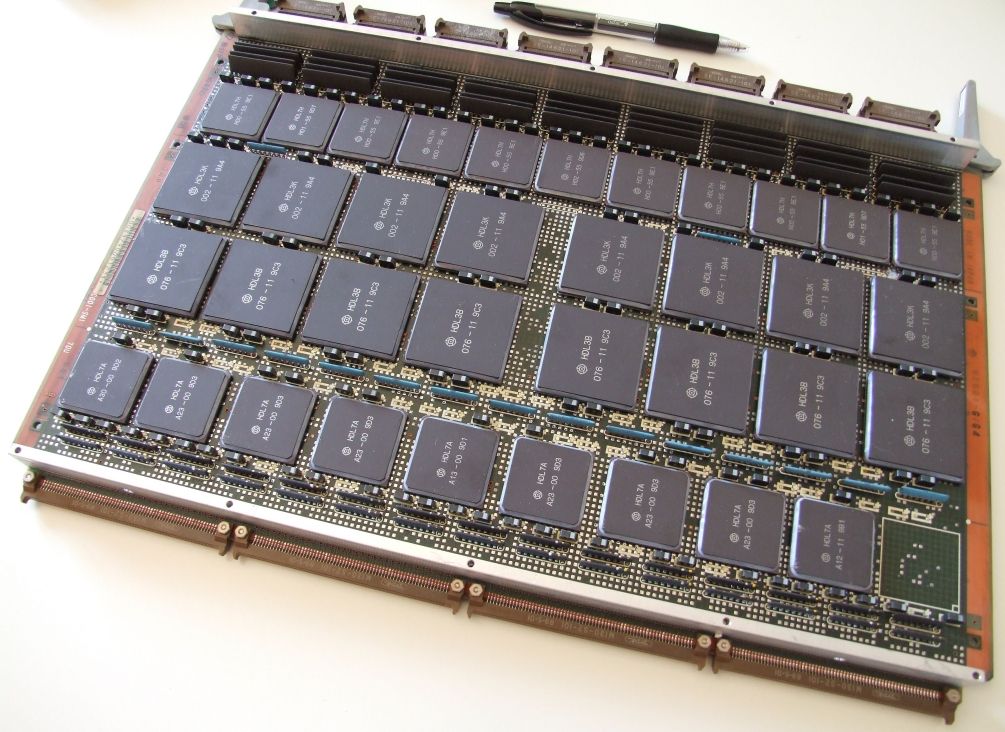

Vista

dall'alto di una scheda di calcolatore Philco Transac S-2000 simile a quella

raffigurata sopra (ma non identica). Si nota la realizzazione modulare, con una

serie (20 o 21) di schedine contenenti due oppure 4 transistor ciascuna saldate

al medesimo circuito stampato (PCB) di base. La CPU dell'S-2000 impiegava un

nuovo tipo di circuito addizionatore (adder) asincrono, concepito per

minimizzare il tempo di propagazione del riporto, sviluppato da tre ingegneri

dell'Institute

for Advanced Study all'inizio degli anni Cinquanta. I vari modelli

dell'S-2000, e precisamente l'iniziale 210 cui seguirono il 211 ed il 212,

vennero commercializzati a partire dal 1957 fino al 1966, anno in cui Philco ne

cessò la produzione, si dimostrarono eccellenti e veloci sia nel calcolo

scientifico che in altre applicazioni. Questi calcolatori erano macchine a 48

bit progettate per eseguire con efficienza operazioni in virgola mobile (floating-point);

la RAM era ampia 64 Kword, con un tempo di accesso di soli 6 microsecondi (due

volte più veloce dell'IBM 7094), poi ulteriormente ridotti a 2 microsecondi nel

1964, valore nettamente migliore di quello del supercalcolatore STRETCH

(E. D. Reilly, Milestones in Computer science and Information technology,

Greenwood Press 2003). Svariati sistemi S-2000 vennero acquistati dal

Dipartimento della Difesa USA ed impiegati ad esempio dall'esercito nei propri

laboratori missilistici (White Sands Missile Range, New Mexico).

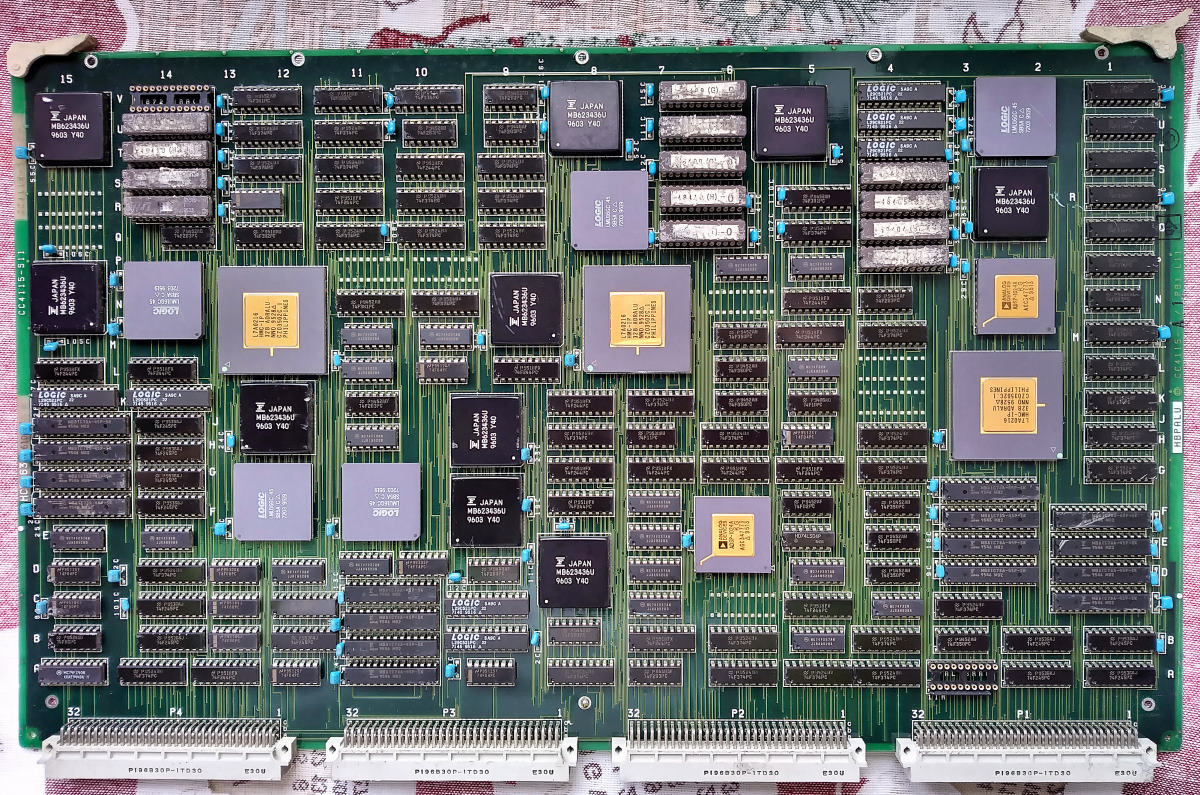

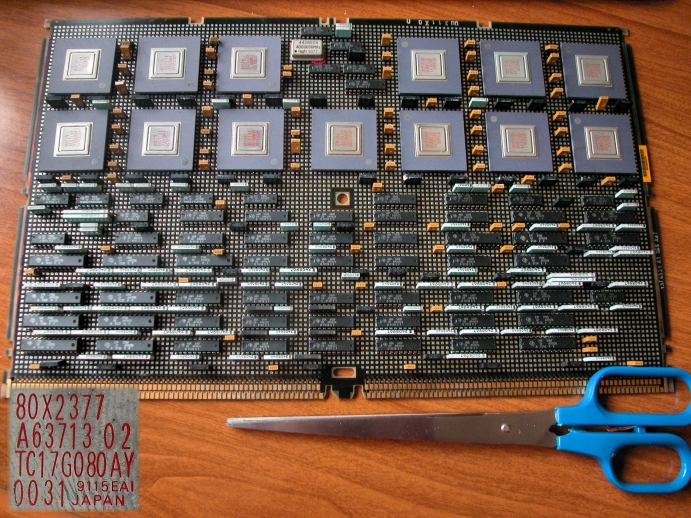

I

calcolatori Philco 2000 impiegavano transistor SBT oppure MADT (Micro-Alloy

Diffused base Transistor) a seconda della frequenza operativa. In particolare il

modello 210 usava gli SBT ed il 211 i MADT. Le schede componenti la CPU, del

tipo di quella raffigurata qui sopra, contenevano fino a 18 transistor l'una. La

maggior parte delle funzioni logiche era ottenuta dalla combinazione di due soli

tipi di circuiti di base, un inverter (basato su transistor SB-102 nel modello

210 e 2N501 nel 211) ed un emitter-follower (SB-102 e, rispettivamente, 2N393).

Il 2N393 è un Micro-Alloy Transistor mentre il 2N501 un vero e proprio

MADT. L'SB-102 è un SBT come un altro transistor impiegato nel modello 210, il

2N345.

Vedi:

http://www.computerhistory.org/collections/accession/102646276;

http://foodman123.com/s2000.htm.

Anche:

http://www.computerhistory.org/brochures/companies.php?alpha=m-p&company=com-42bc217e88ad2.

Anche:

http://computer-refuge.org/bitsavers/pdf/onr/Digital_Computer_Newsletter/Digital_Computer_Newsletter_V10N01_Jan58.pdf.

Anche:

http://www.computinghistorymuseum.org/teaching/lectures/htmllectures/industry/industry_files/frame.htm.

Vedi:

http://ftp.cs.purdue.edu/research/technical_reports/1991/TR%2091-051.pdf.

Anche:

http://www.dtic.mil/cgi-bin/GetTRDoc?AD=AD694624&Location=U2&doc=GetTRDoc.pdf.

Anche:

http://arch.eece.maine.edu/ece574/images/a/af/MainframeComputers.pdf.

Esempi

di calcolatori a 24 o 48 bit: http://www.quadibloc.com/comp/cp0303.htm.

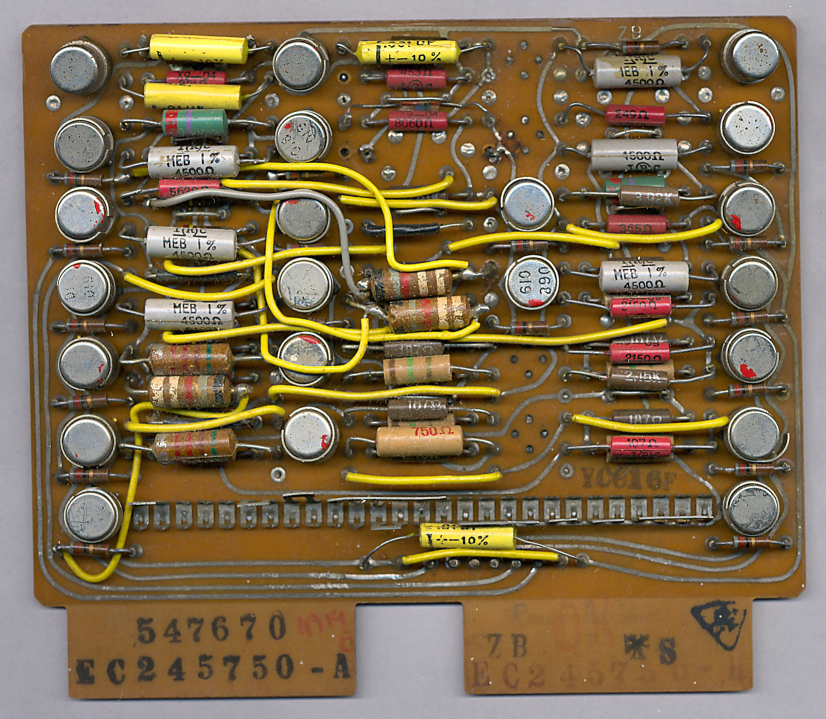

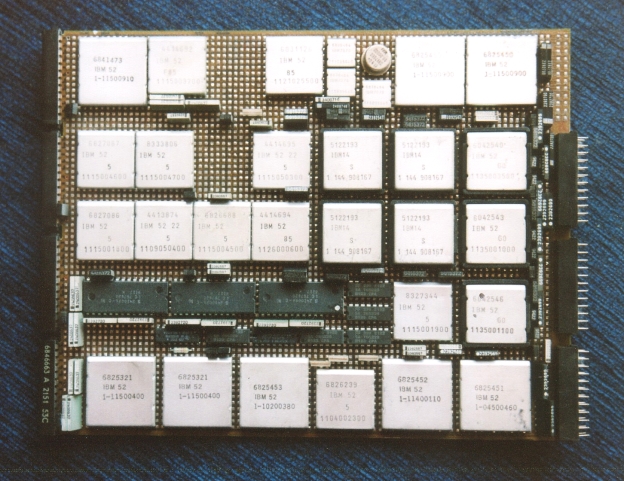

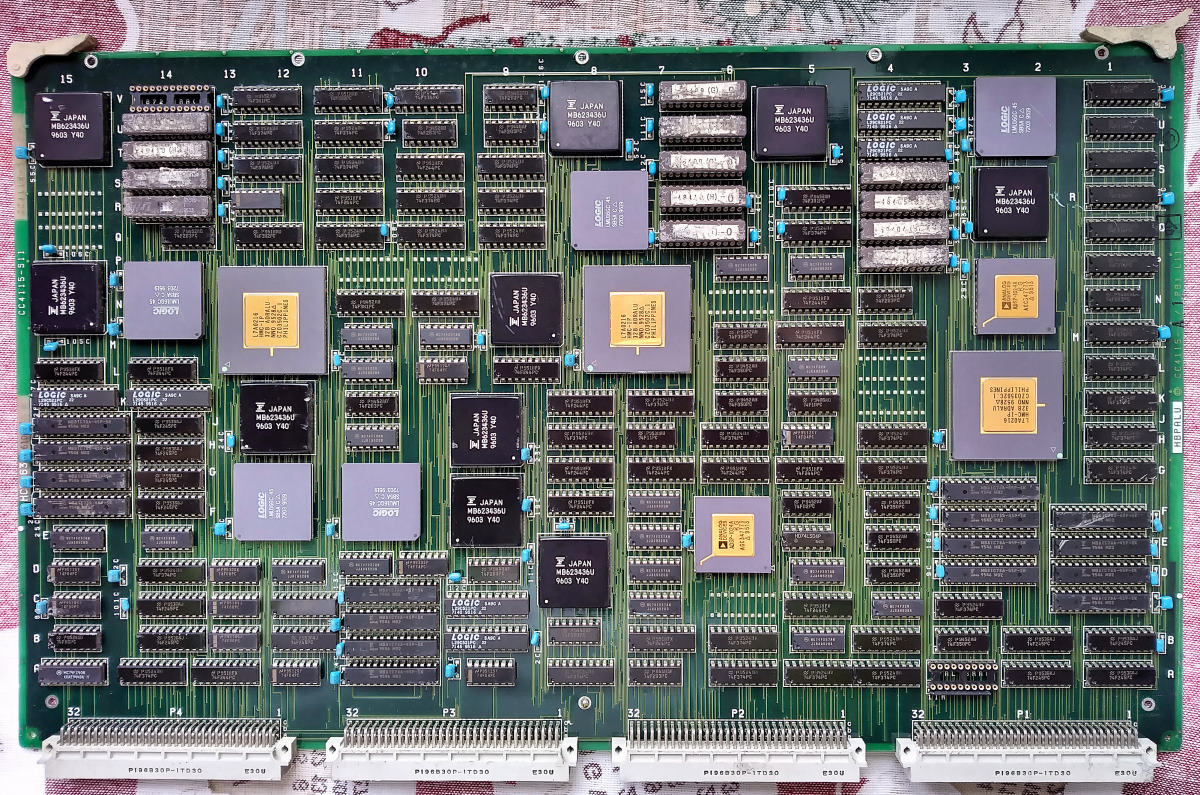

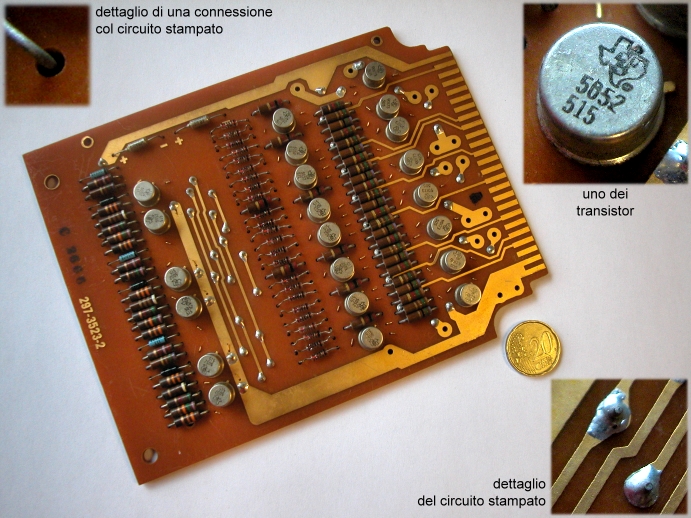

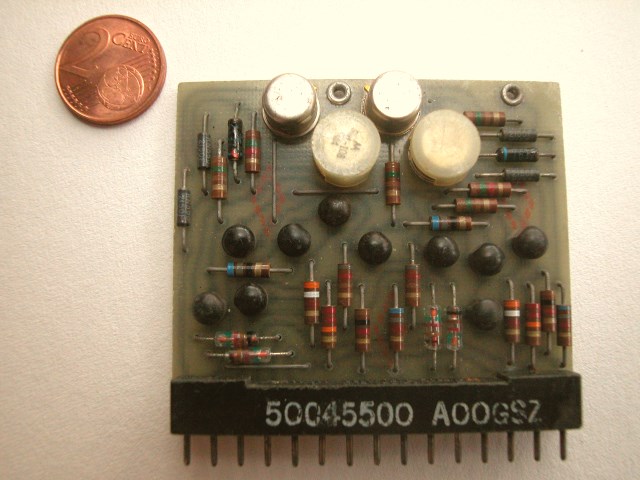

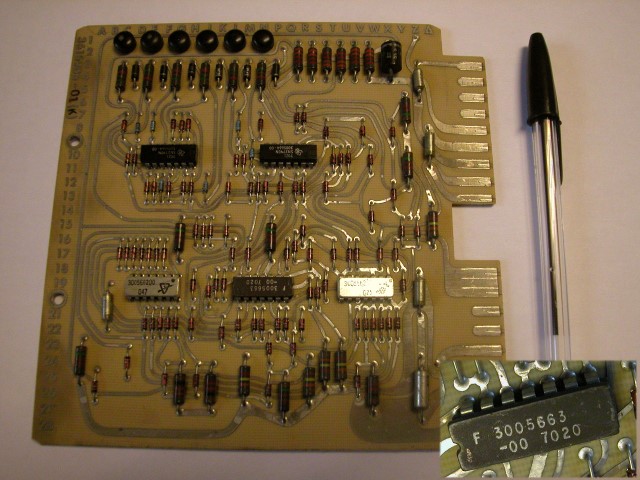

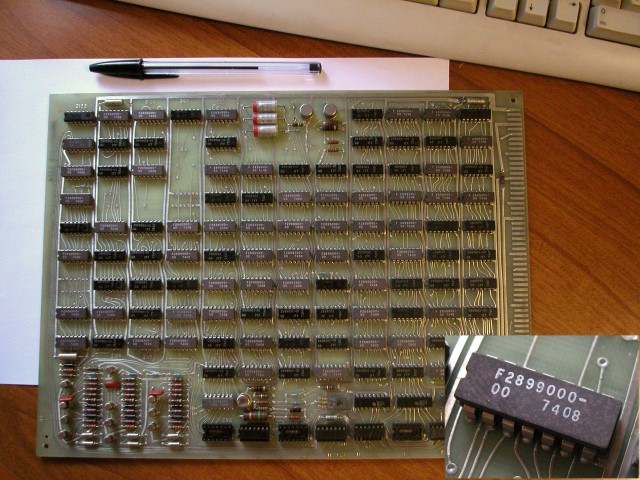

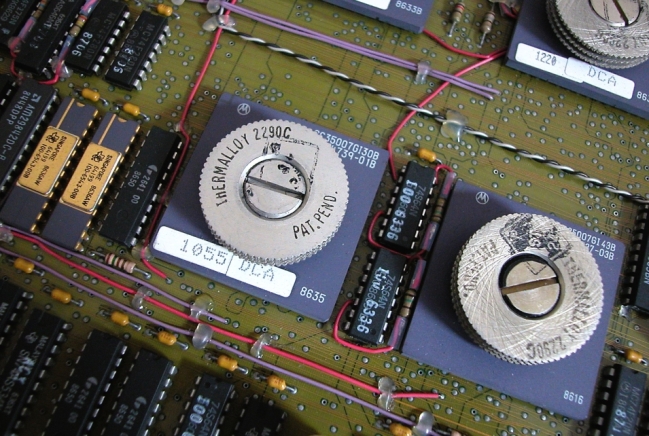

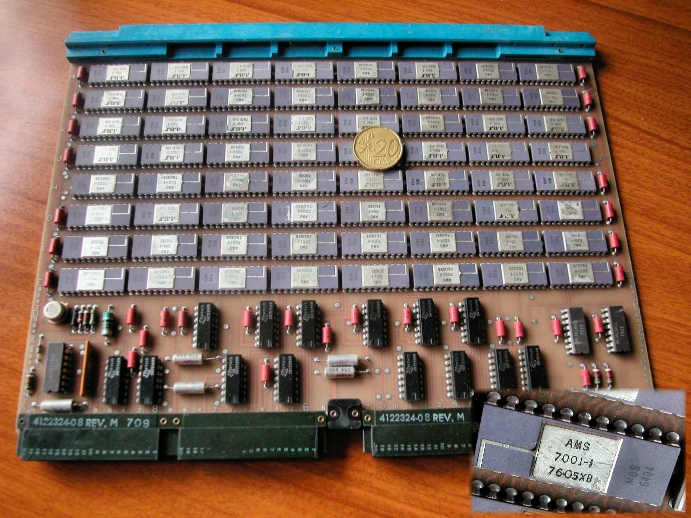

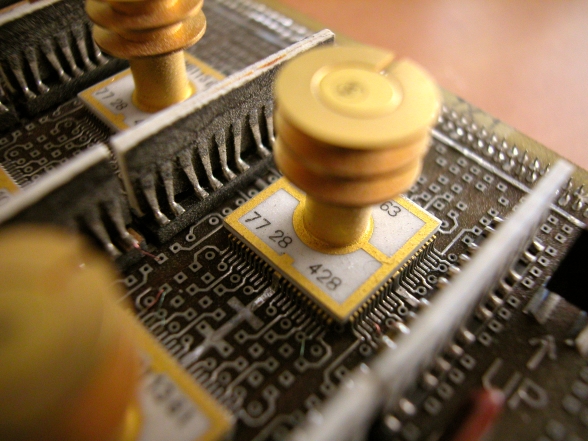

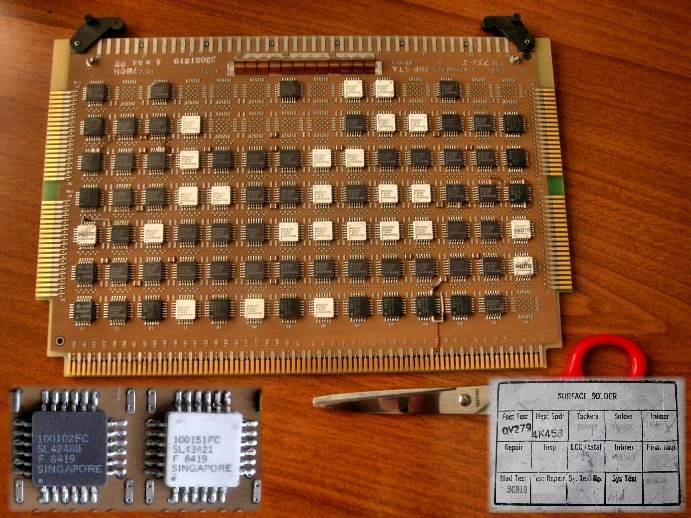

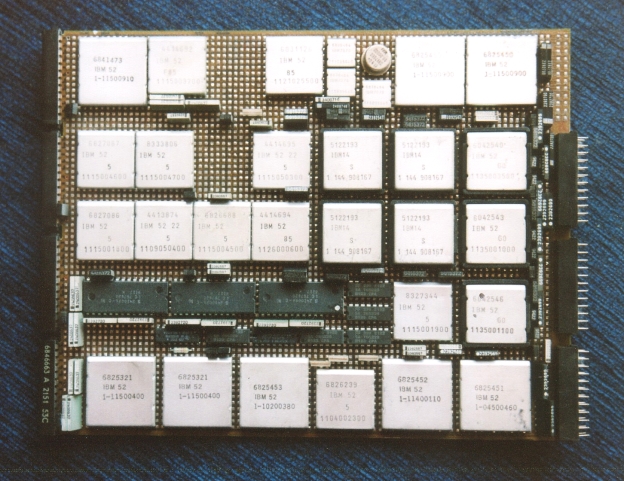

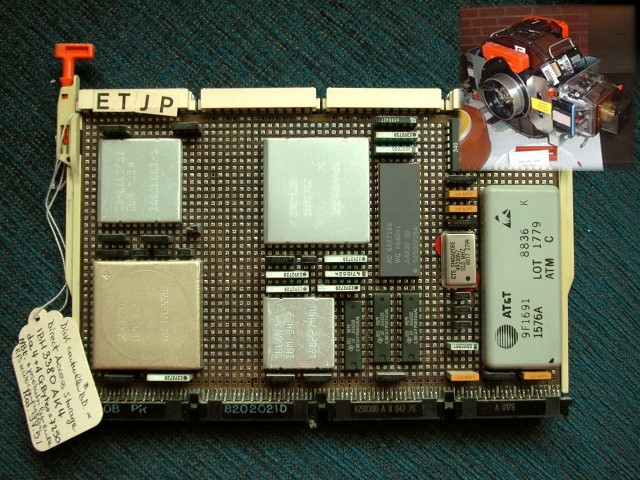

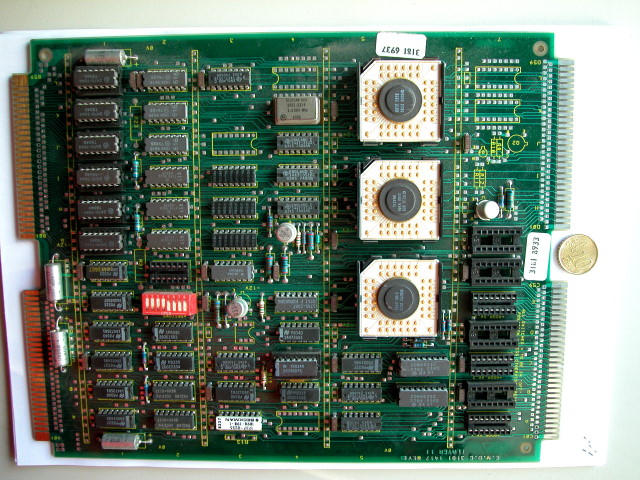

Scheda

di un calcolatore elettronico Philco 212, o S-2000 Model 212

(1963, l'esemplare è del 1965). Questa macchina era un'evoluzione del

calcolatore S-2000 costruita impiegando transistor di tipo FET

(Field-Effect Transistor).

Vedi:

http://ed-thelen.org/comp-hist/philco-212.html.

Anche:

http://corphist.computerhistory.org/corphist/documents/doc-472a31a31c5fb.pdf?PHPSESSID=ccd241....

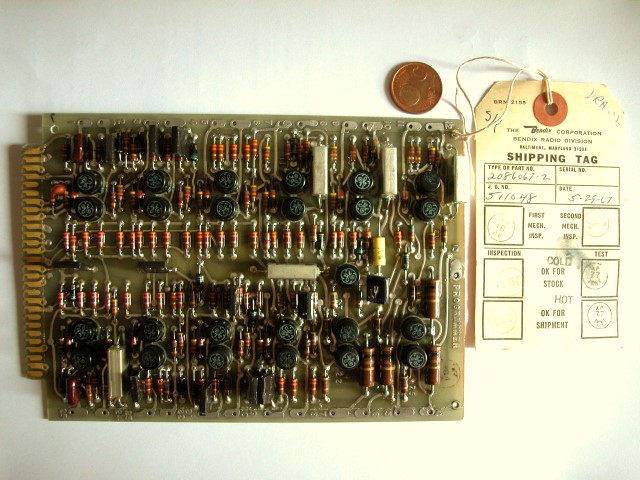

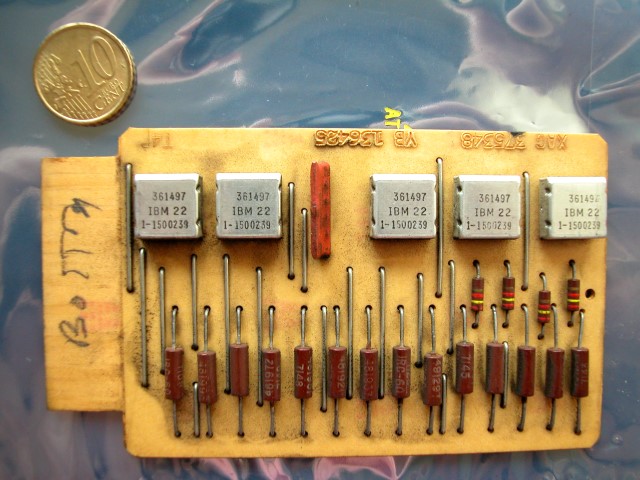

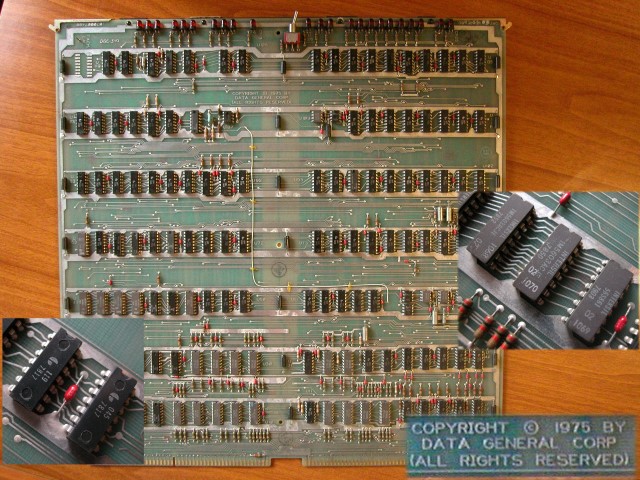

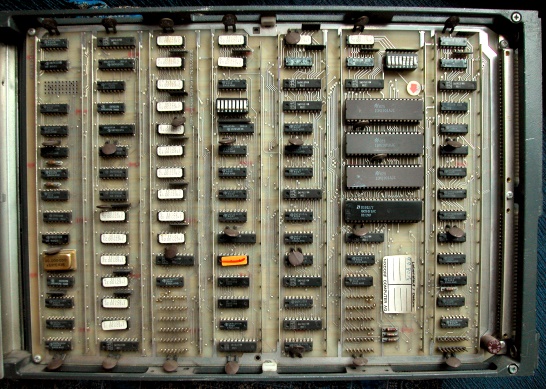

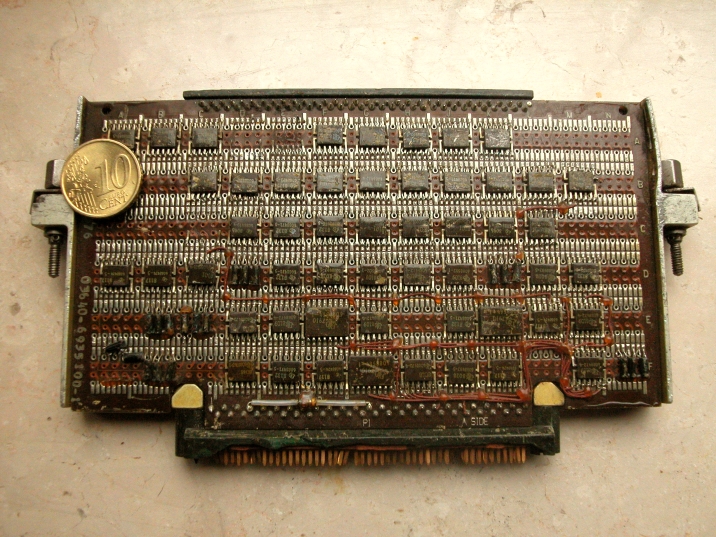

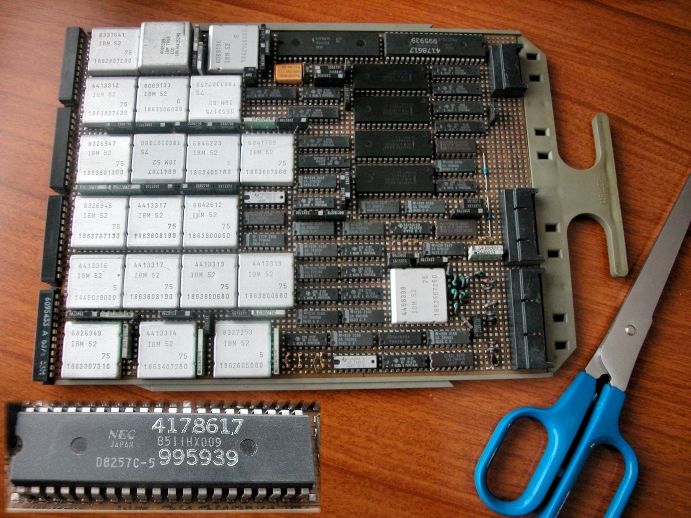

Tre

schede del 1964, o forse 1962, appartenute ad un calcolatore UNIVAC a

transistor. Montano transistor al Germanio fabbricati da RCA e da Western

Electric (v.: http://www.geocities.jp/craft_3/Semiconductor/SONY_Transistor/sony_tr.html). Una

scheda UNIVAC dello stesso formato contenente però valvole anziché transistor

è raffigurata qui.

E' probabile che appartenessero ad un UNIVAC 1105.

Vedi

anche: http://members.fortunecity.com/drg45nzp/boards.html.

Altro

esempio di schede UNIVAC a transistor dei primi anni Sessanta, con transistor

NPN a giunzione al Silicio (vedi dettaglio in basso a destra), equivalenti ai

Texas Instruments 903 (introdotti nel 1954).

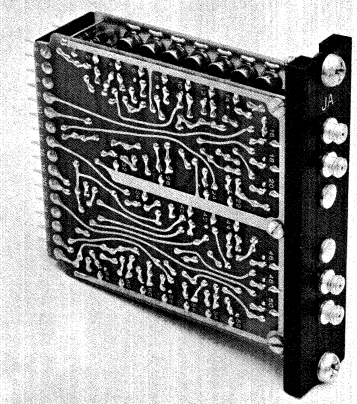

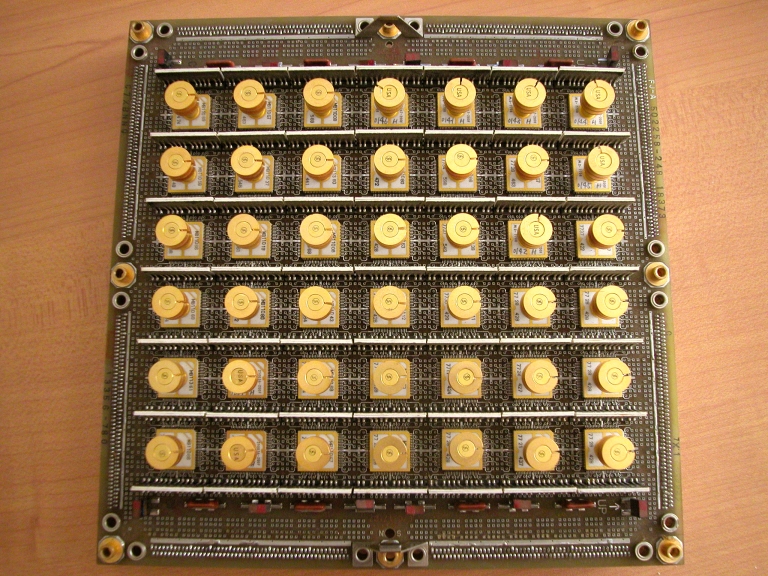

Moduli

cordwood della CPU di un calcolatore Burroughs B5000 (1961, questi

esemplari sono del 1964). Il B5000, calcolatore di seconda generazione a

transistor, è stato una macchina rivoluzionaria sotto molti aspetti, il primo

dei quali consiste nell'essere stato progettato tenendo conto delle esigenze e

delle caratteristiche desiderabili del software (sistema operativo e programmi).

L'hardware del B5000, molto avanzato per l'epoca, incorporava molte soluzioni

all'avanguardia (multi-processing, istruzioni per la manipolazione di stringhe,

protezione della memoria, elevata modularità ecc.) ed era pensato per

supportare al meglio i principali linguaggi di alto livello usati all'epoca

(COBOL e ALGOL); questo calcolatore è stato, fra l'altro, il

primo computer commerciale dotato di un meccanismo di memoria virtuale

effettivamente funzionante. L'architettura di sistema del B5000 è stata

replicata ed estesa da Burroughs e poi da Unisys nei successivi 25 anni,

diventando così una fra le architetture più longeve nella storia

dell'informatica.

Multiprocessors

introduced during 1960s incuded the B5000 series (2 processors in 1963), the GE

645 (4 processors in 1965), the UNIVAC 1108 (3 processors in 1965), and the IBM

System/360 model 67 (2 processors in 1967).

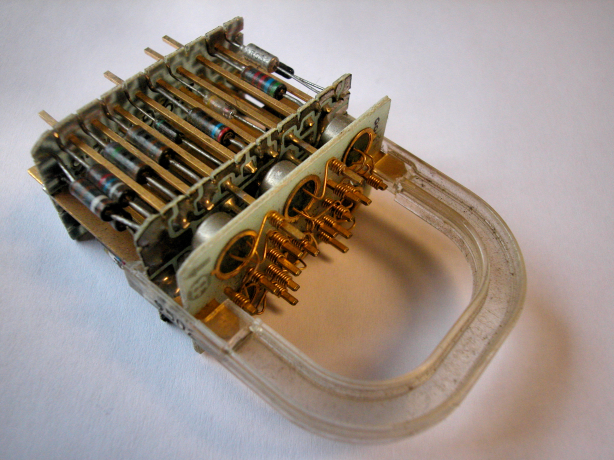

Dettaglio

di un modulo del B5000, realizzato con tecnica cordwood di derivazione militare.

Contiene 6 transistor. Lo stesso tipo di moduli è usato anche nei calcolatori

Burroughs della serie B200 (vedi http://www.smecc.org/burroughs_b-200.htm).

Sull'architettura

del B5000 e dei suoi discendenti: http://www.ajwm.net/amayer/papers/B5000.html.

Anche:

http://special.lib.umn.edu/cbi/oh/pdf.phtml?id=21;

http://www.ardenstone.com/projects/cs63/summary.php.

Anche

(conciso e ben fatto): http://www.tomshw.it/cpu.php?guide=20090611.

Sulle

macchine Burroughs: http://www.retrocomputingtasmania.com/home/projects/burroughs-b6700-mainframe.

Annuncio

del B5000 (Febbraio 1961): http://www.computer.org/portal/web/csdl/doi/10.1109/mahc.1987.10007.

Caratteristiche

del B5000 e di altri calcolatori di "seconda generazione": http://ed-thelen.org/comp-hist/BRL64-b.html.

Foto

di un modulo simile a questi: http://www.democraticunderground.com/discuss/duboard.php?az=view_all&address=105x7118906.

Vedi:

W. Lonergan, P. King, Design of the B 5000 system, in Bell, Newell, Computer

structures: readings and examples, McGraw-Hill 1971, pp. 267-273.

Modulo

della CPU di un calcolatore Burroughs B6500 (1966), direttamente derivato

dal B5000.

Vedi:

http://www.cs.ucf.edu/~eurip/papers/BurroughsB6500stack.pdf.

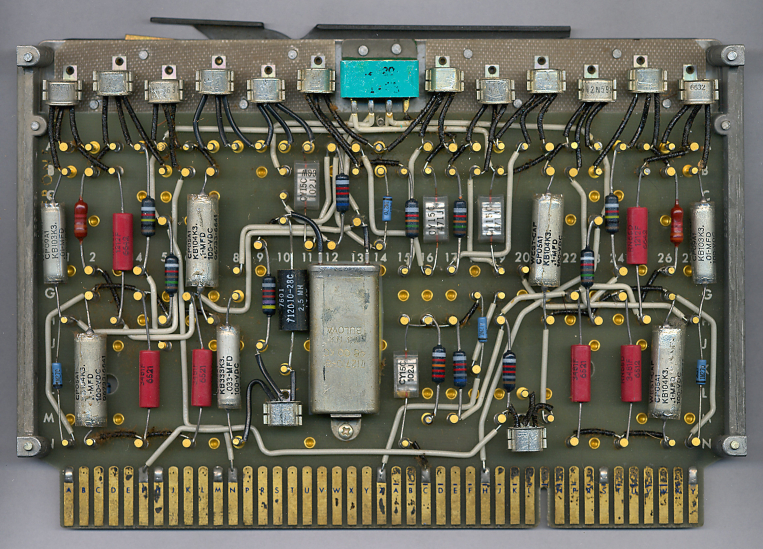

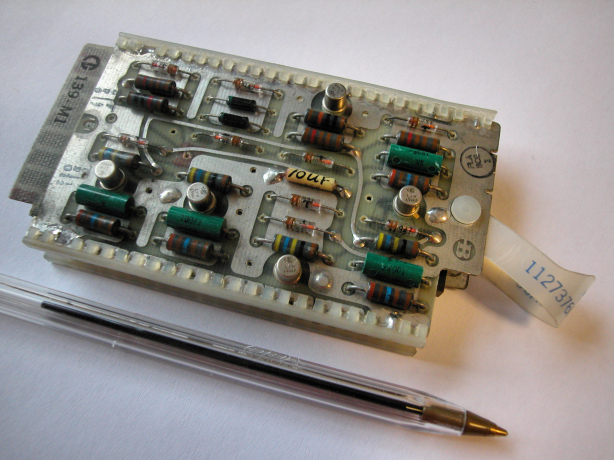

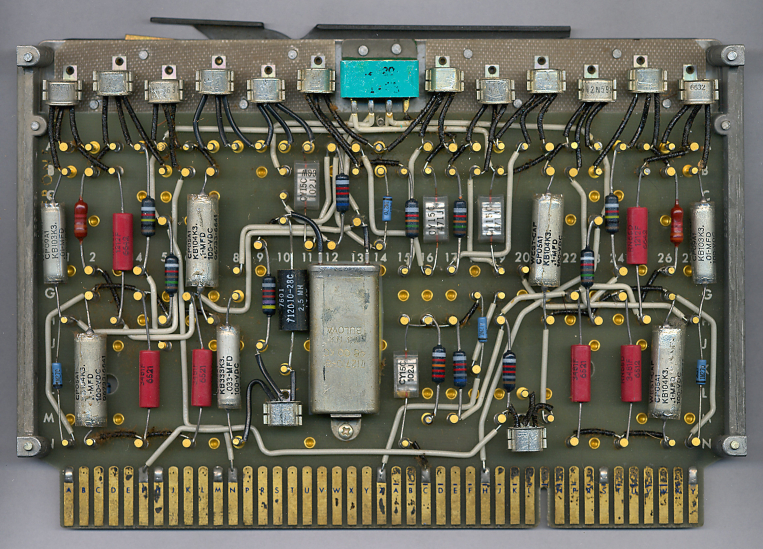

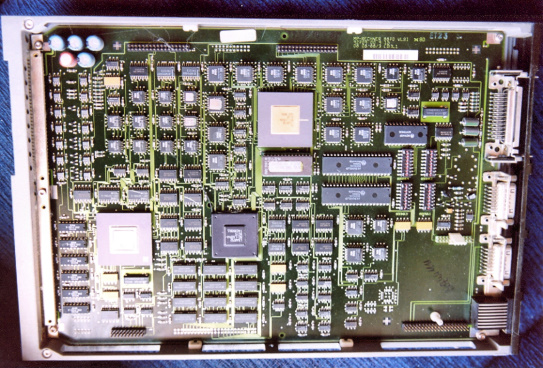

Scheda

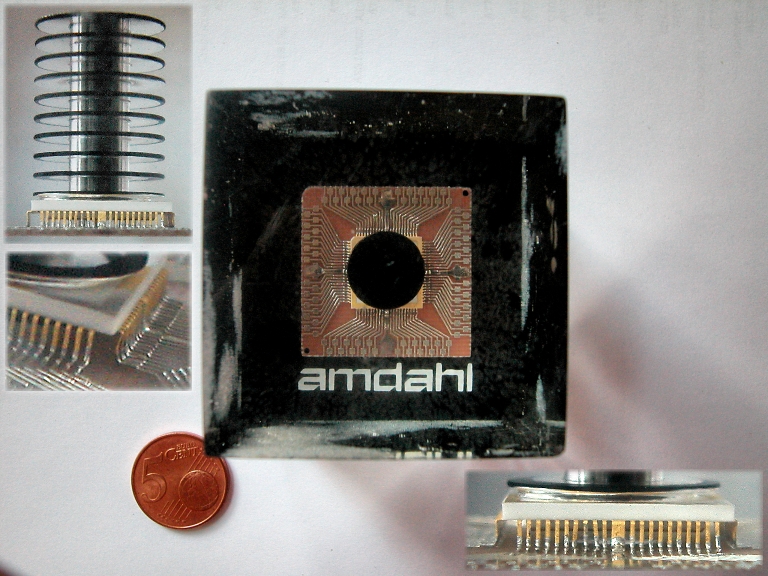

di calcolatore IBM 7030 "Stretch" (1961). Il 7030

è stato il primo supercalcolatore IBM e, fino al 1964 (introduzione del CDC

6600) il più veloce calcolatore elettronico esistente. Questa macchina nasce da

una specifica richiesta fatta nel 1954 alla UNIVAC e alla IBM dal Lawrence

Livermore Radiation Laboratory dell'Università della California, ed in

particolare da Edward

Teller, che aveva bisogno di un nuovo e potente computer per l'esecuzione di

complessi calcoli di idrodinamica tridimensionale (calcoli necessari allo

sviluppo di bombe termonucleari). Ci si attendeva una macchina dal costo pari a

circa 2,5 milioni di Dollari con una velocità di calcolo compresa tra 1 e 2

MIPS, valore elevatissimo per l'epoca. Al progetto lavorò, presso gli

stabilimenti IBM di Poughkeepsie, un team di ingegneri del quale faceva parte

anche Gene Amdahl. L'IBM

si discostò notevolmente dalle richieste originarie, sviluppando una macchina

molto più potente (con una velocità stimata di ben 10 MIPS) ma anche più

costosa della previsione iniziale. Ciò spinse l'Università della California a

scegliere il progetto concorrente, cioè quello della UNIVAC, che si

concretizzò nel calcolatore decimale LARC.

Nel 1956 IBM propose quindi il suo nuovo computer ai laboratori di Los Alamos (Los

Alamos Scientific Laboratory, o LASL); lo sviluppo, durante il quale si

decise di impiegare gli allora nuovi e veloci transistor

a diffusione in luogo dei transistor a punte di contatto e degli SBT, durò

fino al 1960, passando attraverso vari ripensamenti e riformulazioni successive,

ad esempio per limitare il numero totale di transistor utilizzati (più di

200.000 nel progetto iniziale). Il contratto con il LASL prevedeva la realizzazione di un

calcolatore con una velocità di circa 4 MIPS, cioè 100 volte più veloce

dell'IBM 704. Il prezzo del 7030 venne fissato a ben 13,5 milioni di Dollari,

un'enormità per quegli anni. Nel 1961, quando il primo esemplare venne

installato presso il LASL, le prestazioni effettive risultarono molto inferiori

alle attese: solamente 1,2 MIPS. A causa di ciò il prezzo venne ridotto a 7,8

milioni di Dollari.

Il

7030 (sopra una sua immagine da questo

link IBM) ebbe uno scarso successo commerciale: ne vennero venduti solo

pochi esemplari (9, per la precisione), la stragrande maggioranza dei quali

negli Stati Uniti. Nonostante ciò questa macchina è storicamente importante

per una serie di ragioni tra cui: 1) è stato il calcolatore nel quale IBM ha

introdotto la tecnologia modulare SMS, ripresa poi in molti altri computer; 2)

è stato il primo grande calcolatore interamente a transistor: ne conteneva

circa 169.000; 3) con esso sono stati introdotti molti concetti ripresi nelle

successive generazioni di calcolatori e tuttora utilizzati: in particolare la

multiprogrammazione, la protezione della memoria, la gestione degli interrupt,

il pipelining

delle istruzioni, la logica

di prefetch ed il memory

interleaving. Il 7030 fa uso della prima generazione di moduli SMS, che

differiscono in svariati aspetti da quelli "classici", più recenti.

Ad esempio, i moduli del 7030 hanno un circuito stampato a due facce e tutti i

transistor che "ospitano" sono disposti su due oppure quattro file.

Una

scheda simile: http://commons.wikimedia.org/wiki/File:IBM_7030_Stretch_circuit_board.jpg.

Sull'IBM

7030: http://www.cs.clemson.edu/~mark/stretch.html

(include una lista dei vari esemplari venduti). Vedere in particolare la sezione

"The Legacy of Stretch" che riguarda l'influsso di questa macchina

sull'architettura dei successivi mainframe IBM.

Anche:

http://archive.computerhistory.org/resources/text/IBM/Stretch/

(vedi in particolare la directory /pdfs).

A

Description of the Stretch: http://archive.computerhistory.org/resources/text/IBM/Stretch/pdfs/05-10/102634114.pdf.

Un

vecchio articolo

di Datamation (1981) che illustra l'eredità architetturale dello Stretch.

Un

articolo

sullo Stretch del Dr. Dobb's Journal (2000).

Anche:

http://www.textfiles.com/bitsavers/pdf/ibm/7030/Bloch_EngrDesOfStretch_1959.pdf.

Sulla

memoria virtuale nello Stretch: http://www.textfiles.com/bitsavers/pdf/ibm/7030/1959_fallJCC.pdf.

Anche:

http://www.brouhaha.com/~eric/retrocomputing/ibm/stretch/.

Anche:

http://www-03.ibm.com/ibm/history/exhibits/mainframe/mainframe_PP7030.html.

Una

descrizione completa dello Stretch, comprendente dettagli e foto relativi

all'organizzazione dei circuiti è contenuta nell'articolo The engineering

design of the Stretch computer di E. Bloch, in Bell e Newell, Computer

structures: readings and examples, McGraw-Hill 1971, pp. 421-439.

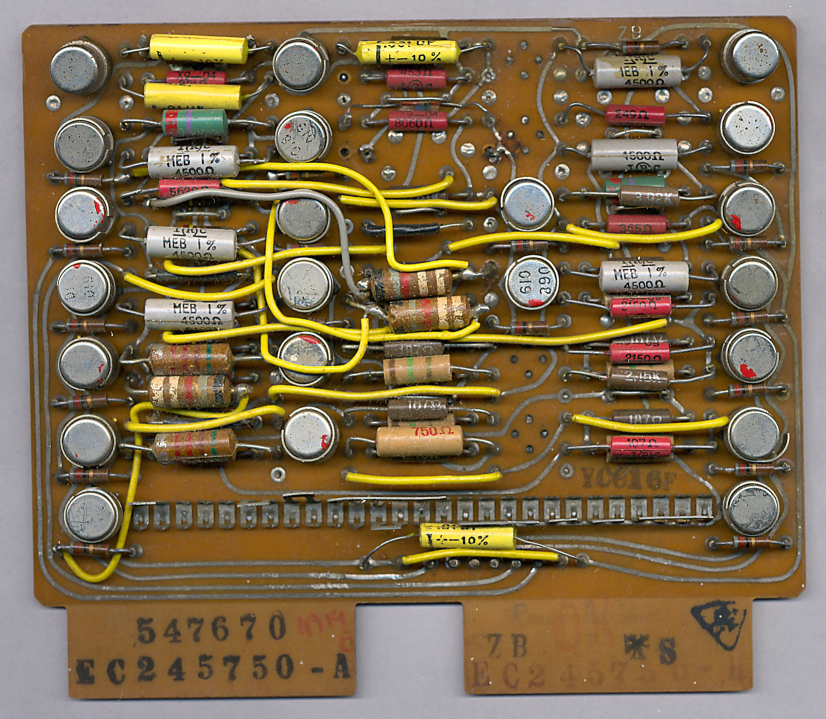

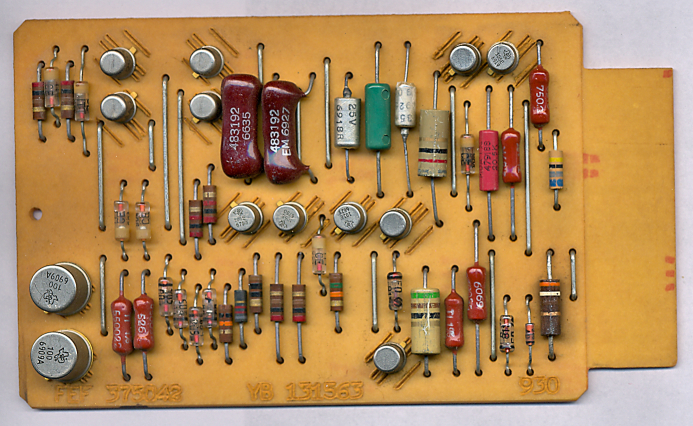

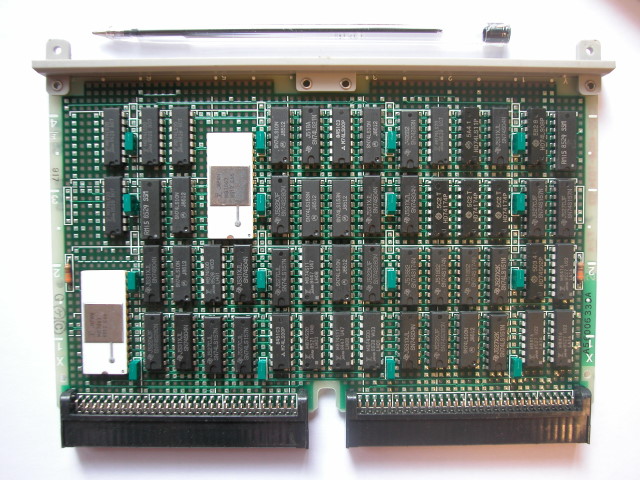

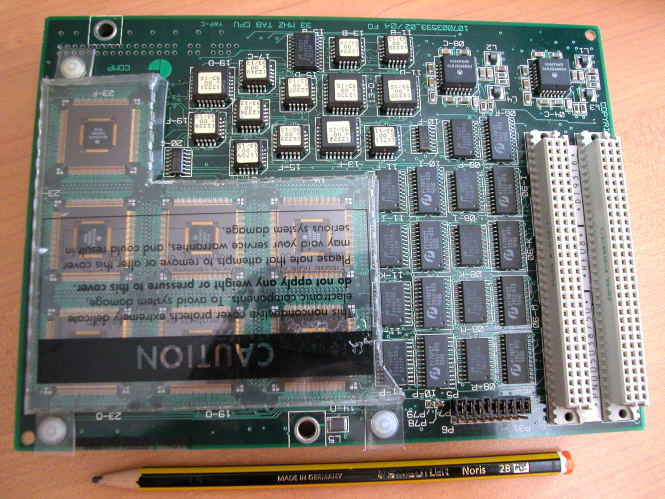

Scheda

(o modulo) IBM in standard SMS (Standard Modular System). Questo

esemplare è del 1969. Lo standard SMS ha rappresentato uno dei primi tentativi

di standardizzazione dei circuiti impiegati nei calcolatori elettronici.

Introdotto col calcolatore IBM

7030 "Stretch", il primo computer IBM a transistor, è rimasto in

uso fino alla fine degli anni Sessanta ed è stato utilizzato in molte altre

macchine (608, 1400,

1620, 7000).

In tutto furono prodotti più di 2.500 diversi tipi di moduli SMS, sia digitali

(RTL, DTL e TTL) che analogici.

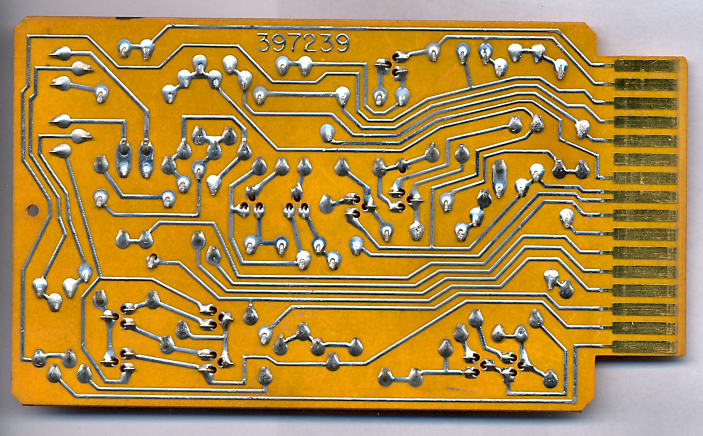

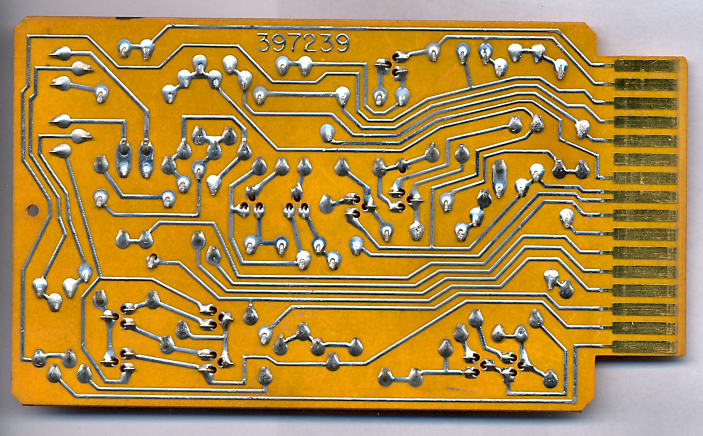

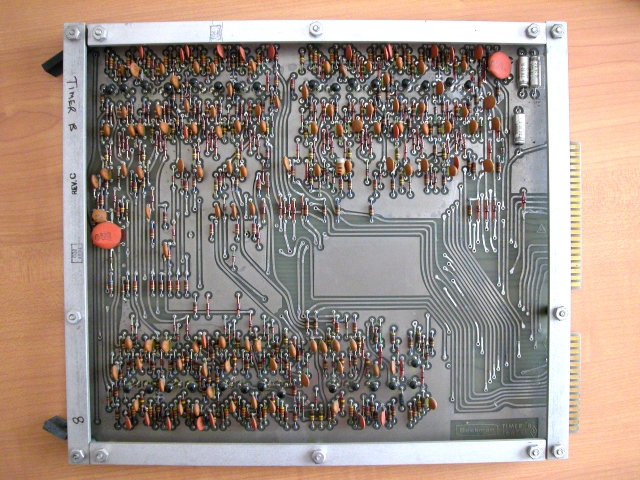

Vista

del retro ("wiring side") del modulo SMS raffigurato sopra. Queste

schede hanno una dimensione standard di 4,5 per 2,5 pollici (moduli singoli)

oppure di 5,375 per 4,5 pollici (moduli doppi), con connettore a 16 contatti. Il

circuito stampato è a singolo strato, progettato per il montaggio automatizzato

dei componenti.

Vedi:

http://members.optushome.com.au/intaretro/SMSCards.htm.

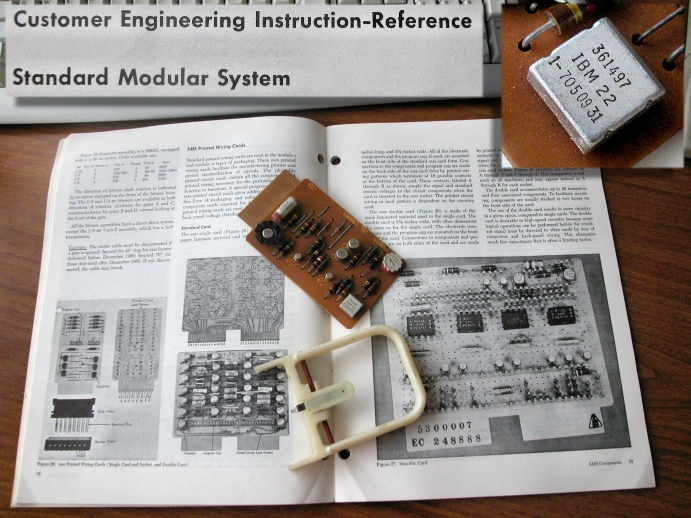

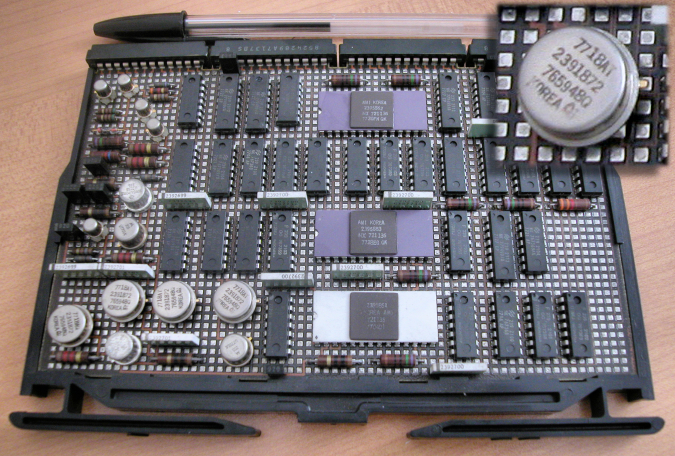

Scheda

IBM SMS (Standard Modular System) ed apposito attrezzo per l'estrazione (SMS

extractor tool) fotografati sullo sfondo di una pubblicazione tecnica IBM del

1962 (SMS Customer Engineering Instruction-Reference). La scheda contiene anche

un modulo SLT (Solid Logic Technology), riprodotto in dettaglio in alto a

destra.

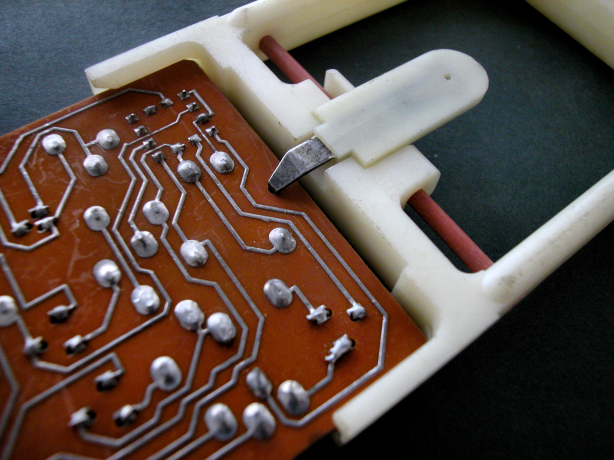

Dettaglio

dell'accoppiamento estrattore/scheda SMS.

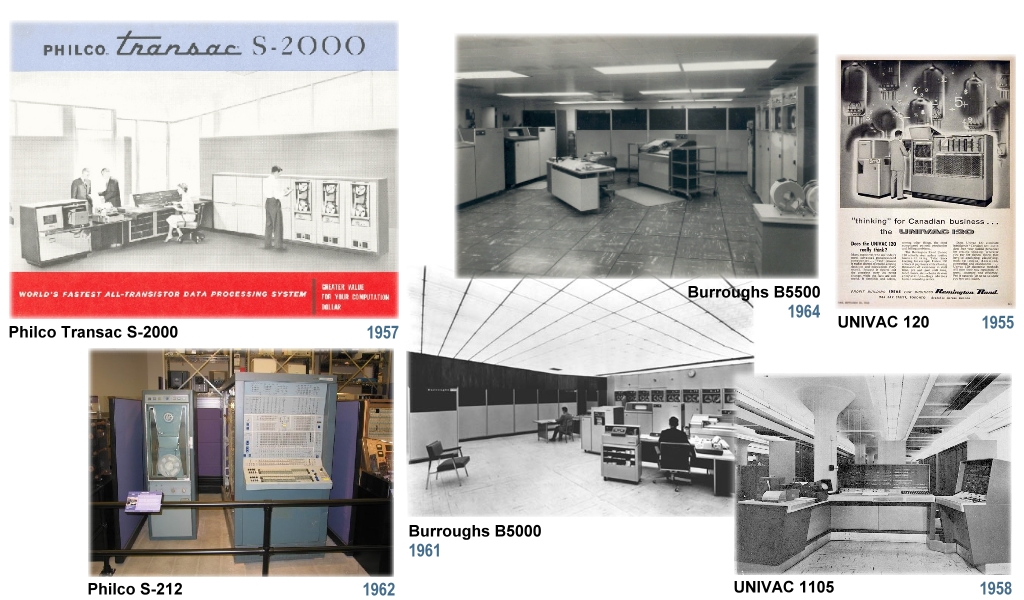

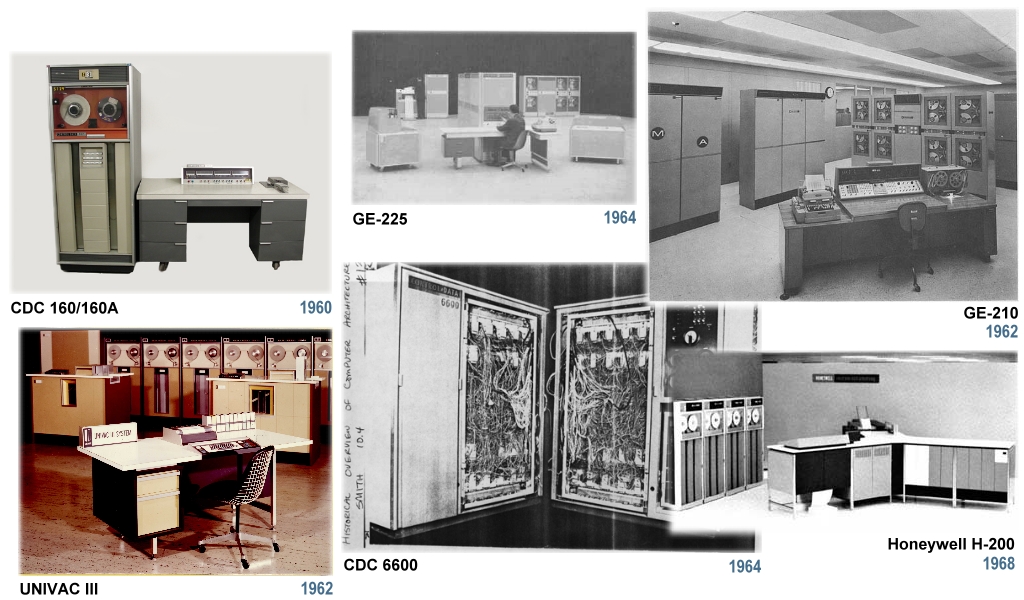

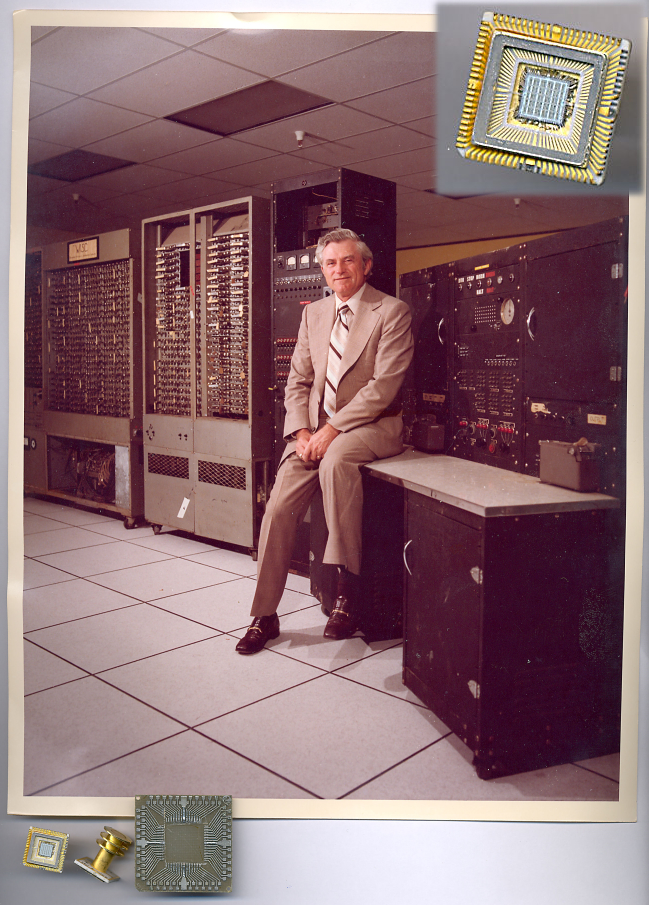

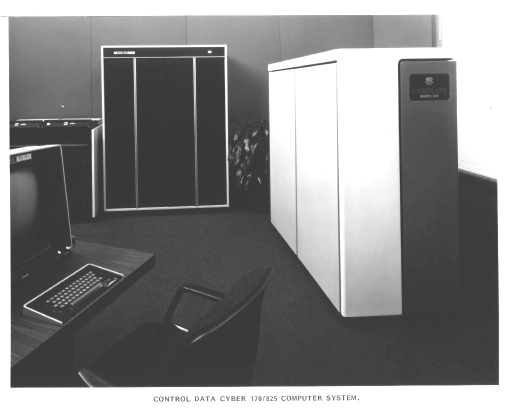

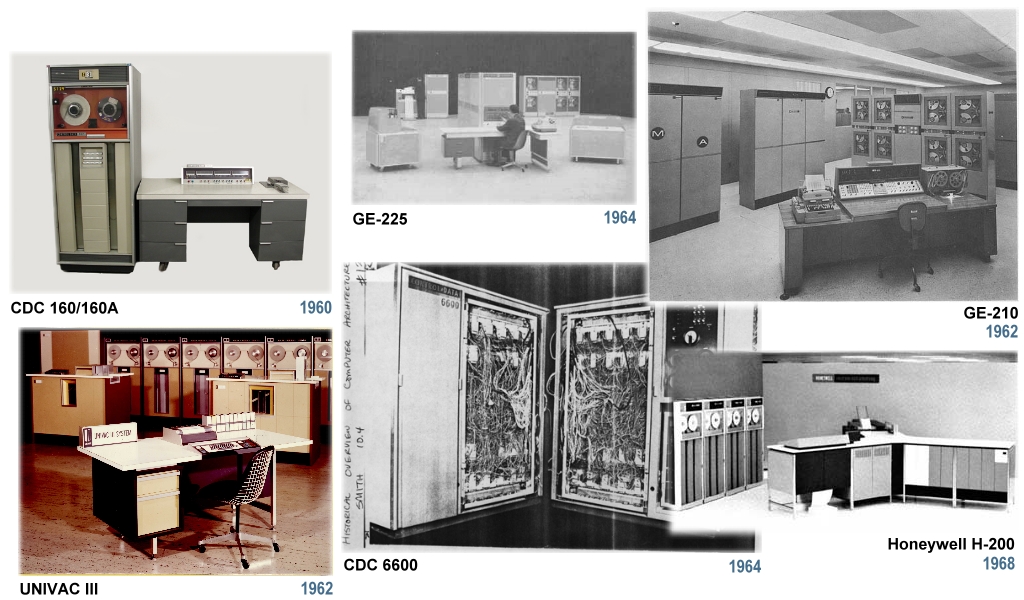

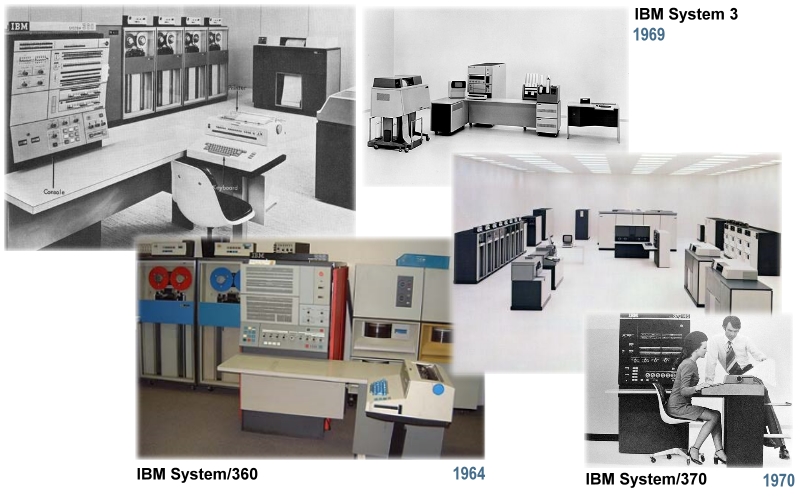

Alcune

delle macchine di cui si parla in questa pagina.

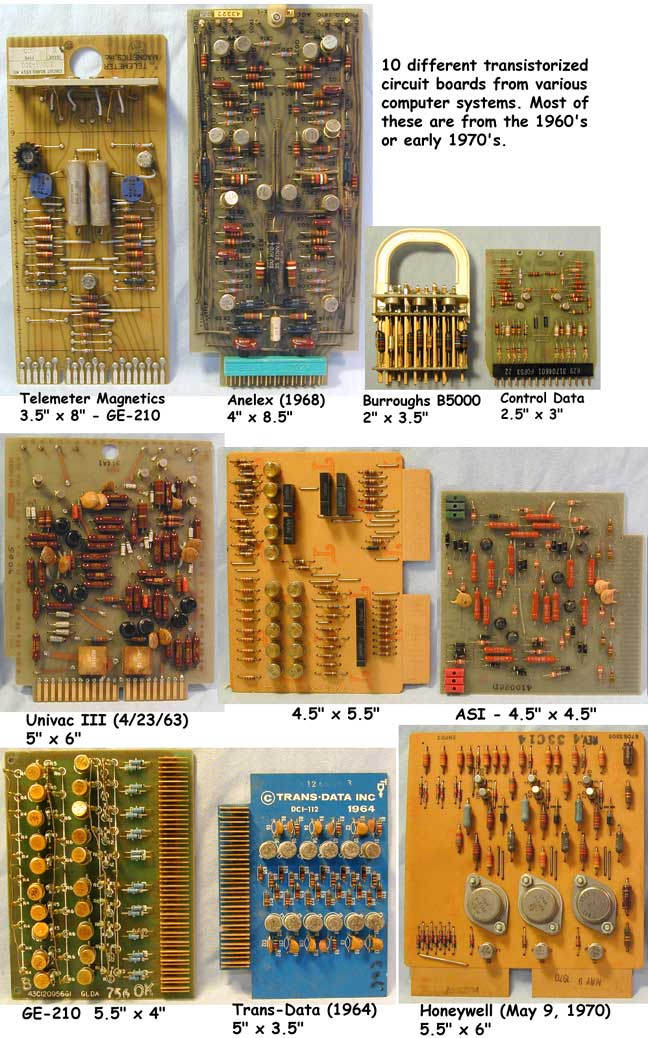

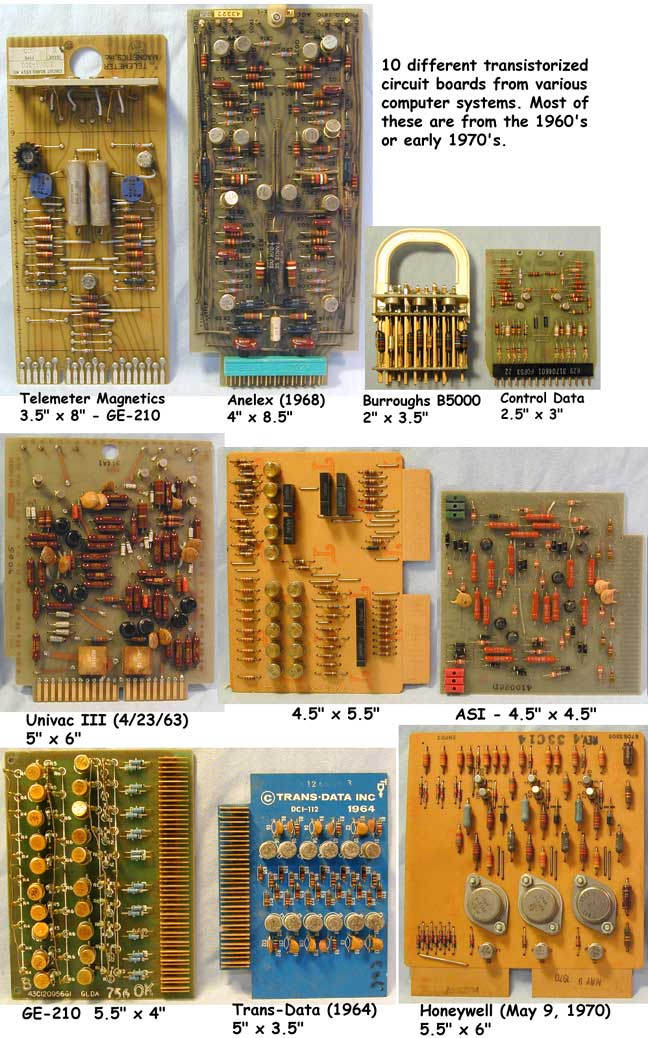

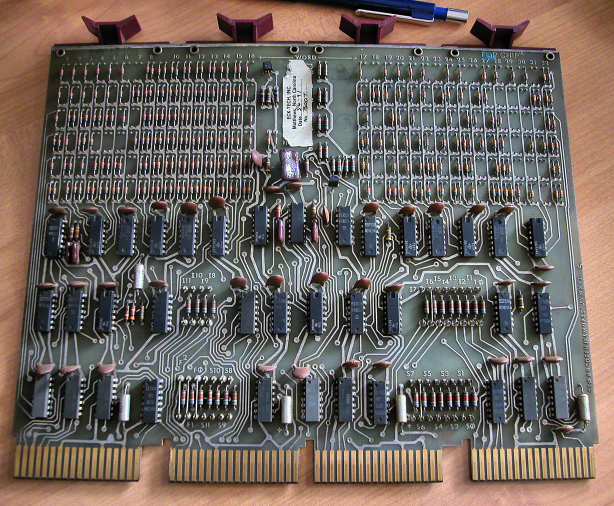

Dieci

esempi di schede a transistor la maggior parte delle quali appartiene a macchine

fabbricate negli anni Sessanta. La Telemeter Magnetics, Inc. (TMI) è

stata uno dei primi fabbricanti di memorie a nuclei magnetici; nel 1962 venne

assorbita dalla Ampex (vedi http://ed-thelen.org/comp-hist/vs-magnetic-core.html,

oppure questa

pagina, oppure questo PDF

con la riproduzione del Digital Computer Newsletter, Luglio 1956). La Anelex

è stata per decenni un famoso fabbricante di stampanti ad alta velocità (vedi:

http://www.cartridgesave.co.uk/news/6-massive-old-school-printers-how-they-were-advertised/).

Del Burroughs B5000 si è già detto più sopra. La schedina CDC ospita

un doppio flip-flop ed è stata fabbricata nel 1964 (apparteneva ad un CDC

3300, vedi più sotto). L'UNIVAC III (1960/2) era la versione a

transistor del calcolatore UNIVAC (anche noto come UNIVAC-I). Maggiori

informazioni su questa macchina si trovano qui: http://jwstephens.com/univac3/page_01.htm

oppure anche qui: http://jwstephens.com/univac3/Univac3-uhn.html.

Il sito bitsavers.org contiene alcuni documenti in PDF che la riguardano: http://www.bitsavers.org/pdf/univac/univac3/.

Il General Electric GE-210 (1962) è un membro della famiglia di

mainframe commerciali GE-200. In sintesi questa macchina è una versione ridotta

ed economica del più potente GE-225, rispetto al quale ha meno canali di I/O e

una RAM più piccola. Il GE-210 è descritto in questa pagina: http://archive.computerhistory.org/resources/text/GE/GE.210.1960.102646284.pdf.

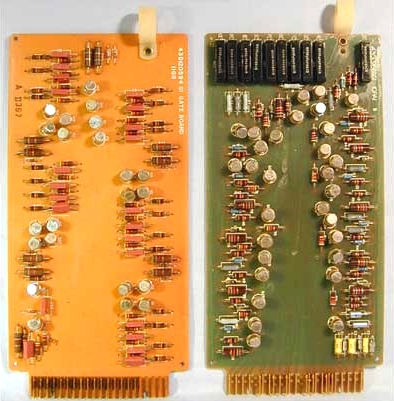

Altre

due schede General Electric (GE) del 1966. Dovrebbero appartenere ad un

calcolatore GE-225, introdotto nel 1965 (vedi: http://ed-thelen.org/EarlyGE-Computers.html,

http://ed-thelen.org/comp-hist/GE225.html).

Schede dello stesso tipo sono anche state utilizzate nel GE-235.

Caratteristiche

di molti computer della "prima" e "seconda generazione": http://ed-thelen.org/comp-hist/AdamsReport1967Q1-2.pdf.

Vedi

(GE-210 e scheda Telemeter Magnetics): http://www.smecc.org/g_e__200_series_computers.htm.

Un'interessante

pagina di discussione sulle RAM a nuclei: http://www.radiomuseum.org/forum/ferrite_core_memory_some_history.html.

Anche

(GE-210 e serie GE-200): http://ed-thelen.org/comp-hist/BRL61-g.html;

http://www.feb-patrimoine.com/projet/ge200/ge200.htm.

Anche

(mainframe General Electric degli anni Sessanta): http://www.computerhistory.org/brochures/companies.php?alpha=g-i.

Una

memoria a nuclei dell'UNIVAC III: http://www.computermuseum.li/Testpage/UNIVAC-III-corememory.htm.

Sempre

sull'UNIVAC III e sui sistemi UNIVAC, vedi questa

pagina (Google Books).

Anche:

http://michelsoft.net/ct/itcurriculum/overview/univac.html;

http://vipclubmn.org/Documents/CommlCPUs.pdf.

Anche:

http://vipclubmn.org/Documents/CommlCustomers.pdf.

Interessante

pagina che fa "rivivere" una memoria dell'UNIVAC III: http://www.holmea.demon.co.uk/Core/Flipper.htm.

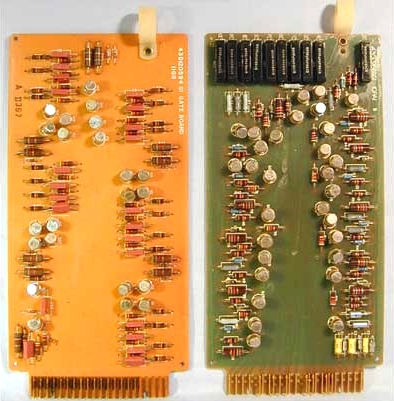

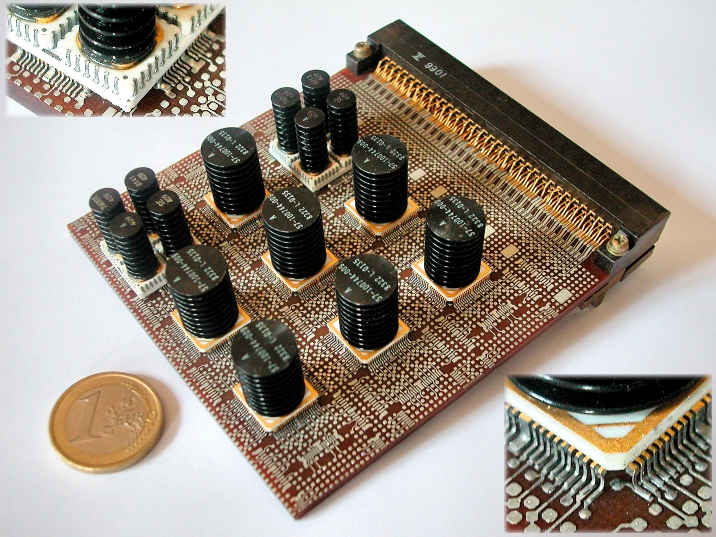

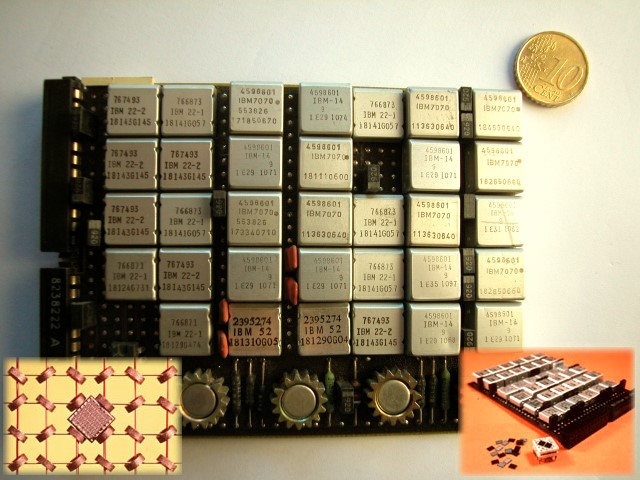

Modulo

contenente due schede appartenuto ad un Communication Processor di Control Data

Corporation (CDC), 1964, con transistor discreti al Silicio.

Una

delle 32 schede a transistor costituenti l’elettronica di una calcolatrice Wang

Series 300 (1965, vedi).

Vedi:

http://www.oldcalculatormuseum.com/wang360.html;

http://www.science.uva.nl/museum/Wang300.html.

Anche:

http://www.xnumber.com/xnumber/wang.htm.

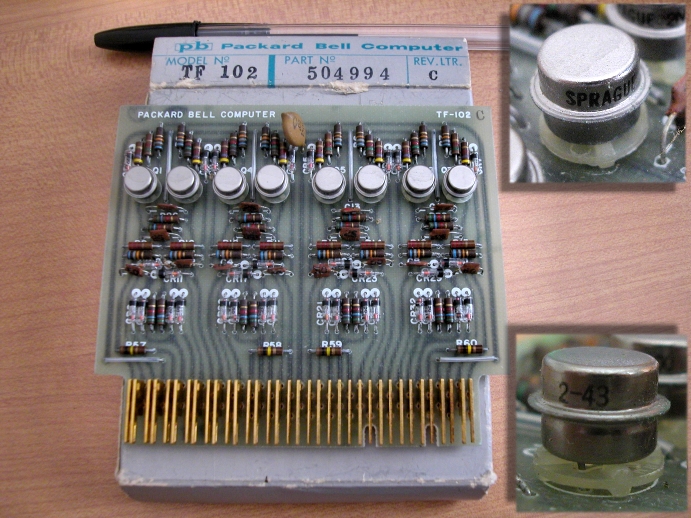

Scheda

di calcolatore elettronico Packard Bell (1966) con 8 transistor

fabbricati da Sprague (vedi dettagli a destra).

Alla metà degli anni Sessanta

(1967, scheda di un calcolatore militare Bendix): i computer di "seconda

generazione" sono realizzati con componenti discreti a stato solido

(transistor, diodi e componenti passivi). Per fare un calcolatore intero

occorrevano centinaia, se non migliaia, di schede come questa, contenenti

ciascuna una ventina circa di transistor.

Vedi: http://www.columbia.edu/acis/history/;

http://history.sandiego.edu/GEN/recording/computer1.html.

Esempio di scheda di

calcolatore militare (1966) a transistor, realizzata col metodo "wire-wrap".

I transistor, tutti fabbricati da Texas Instruments, sono di tipo 2N404 e 2N599

e portano le diciture "USAF CGO" e "JAN CGO".

Una delle schede a

transistor che componevano la CPU di un calcolatore CDC (Control Data

Corporation) 160, un computer usato spesso come terminale per i sistemi CDC

1604 (prima macchina commerciale ad alte prestazioni realizzata interamente a

transistor). La scheda raffigurata qui è del 1965.

Vedi: http://www.cs.virginia.edu/brochure/museum.html.

Anche: http://www.vintchip.com/MAINFRAME/mainframe.html

(interessante collezione di parti di vecchi mainframe).

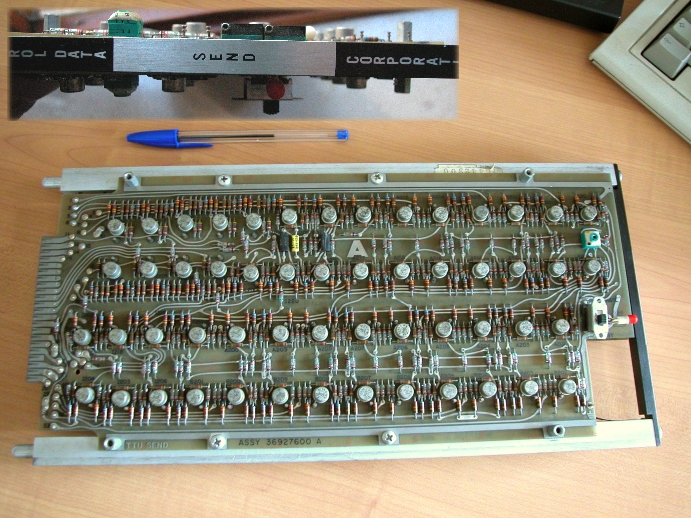

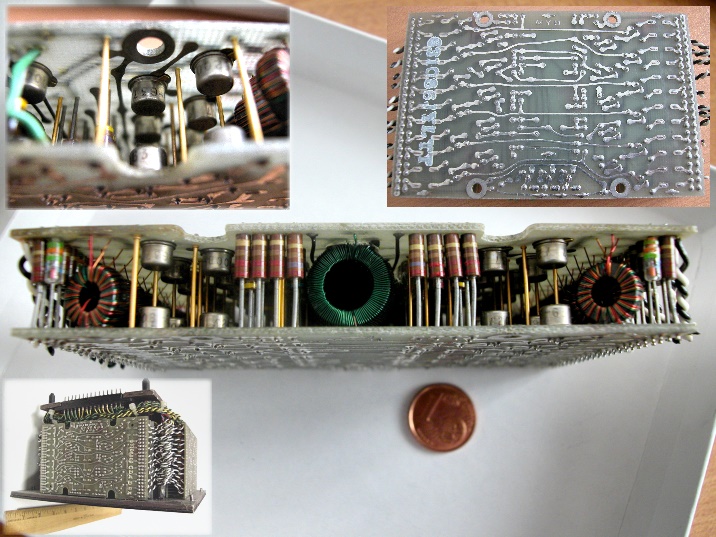

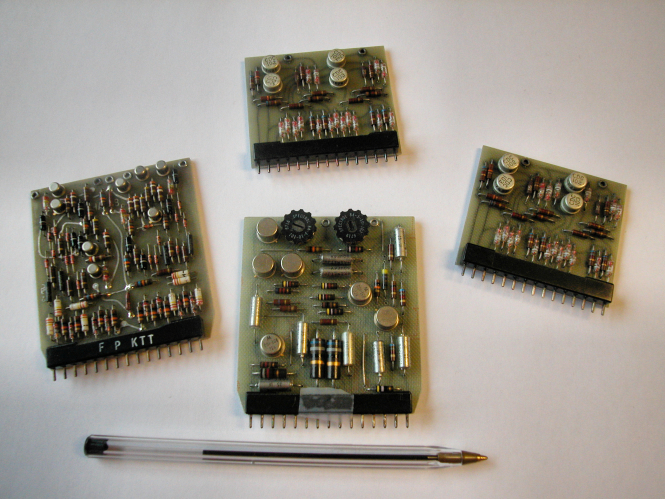

Schede di un

calcolatore CDC 6600 (1966). Il 6600,

progettato da Seymour Cray, introdotto nel 1964 e prodotto fino al 1969, era un

calcolatore di seconda generazione (a transistor) membro della famiglia CDC

6000; viene spesso considerato il

primo supercomputer commerciale (l’IBM STRETCH non può essere

considerato una macchina commerciale). Ne sono stati prodotti in tutto circa 120

esemplari (anche se questa

fonte dice solo 50), una buona parte dei quali è stata acquistata da

laboratori impegnati in ricerche in campo nucleare, soprattutto militare.

Contrariamente ai precedenti calcolatori fabbricati da CDC, come ad esempio i

modelli 1604 e 3000, il 6600 usa transistor a giunzione al Silicio (anziché al

Germanio), fabbricati da Fairchild Semiconductors. In alto a destra si vede un

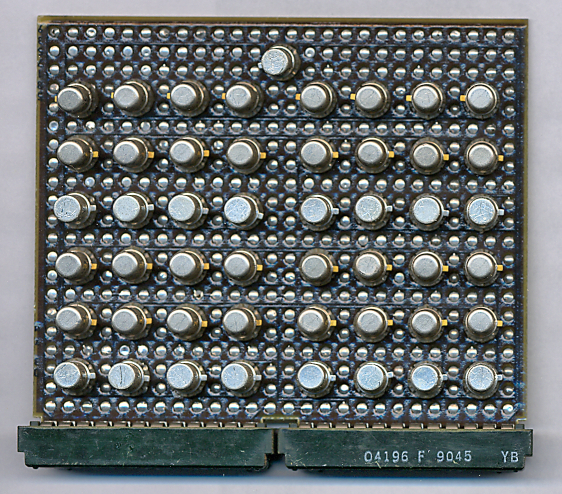

dettaglio di questi transistor, di tipo sub-miniatura. Le schede che formavano

la CPU del 6600 erano riunite a due a due a formare moduli ad alta densità e

facilmente sostituibili; il tutto veniva raffreddato con scambiatori di calore a

freon. La scheda più piccola è invece del tipo di quelle usate nei Peripheral

Processors (PP) del 6600, ovvero dei processori di I/O che affiancavano la CPU

principale del sistema.

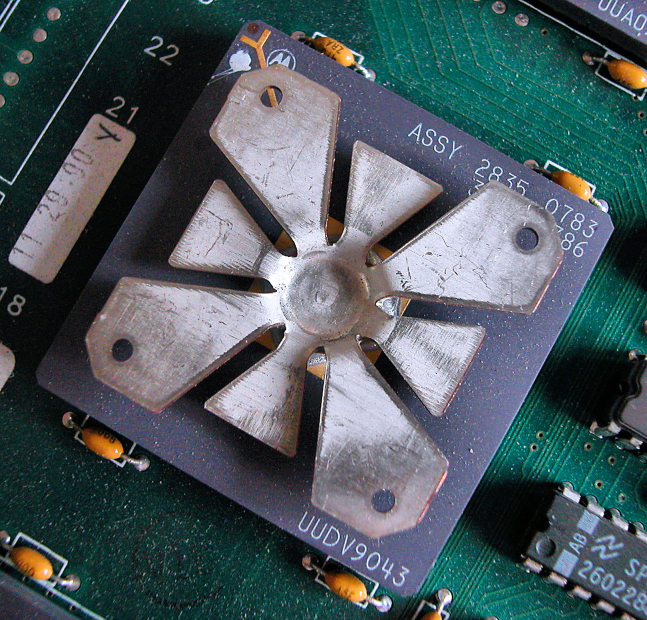

Uno dei moduli logici (cord-wood)

che compongono la CPU del CDC 6600. Contiene due schede del tipo di quelle

raffigurate sopra. Vedi anche qui: http://research.microsoft.com/en-us/um/people/gbell/craytalk/sld034.htm.

Vedi: http://www.cs.virginia.edu/brochure/museum.html;

http://ed-thelen.org/comp-hist/vs-cdc-6600.html

Vedi: http://www.bitsavers.org/pdf/cdc/6x00/books/DesignOfAComputer_CDC6600.pdf.

Vedi: http://www.bitsavers.org/pdf/cdc/6x00/60100000D_6600refMan_Feb67.pdf.

Brochure del 1966 usata

per presentare il CDC 6600 ai potenziali acquirenti: http://ed-thelen.org/comp-hist/6600-humberd-presentation.html.

Vedi: J. E. Thornton, Parallel

operation in the Control Data 6600, in Bell, Newell, Computer structures:

readings and examples, McGraw-Hill 1971, pp. 489-503.

Modulo logico completo

proveniente da un calcolatore CDC 6600, simile a quello descritto sopra.

Modulo cordwood

utilizzato nella memoria di un calcolatore CDC 6600 (1966; nel CDC Cyber

73 è impiegata una memoria analoga - vedi http://www.newbegin.com/html/misc__item_detail_51.html).

In basso a sinistra

un'immagine, tratta dal Web, che mostra la memoria completa (a nuclei magnetici). La tecnica "cordwood", in auge negli anni Cinquanta e

Sessanta, consentiva di contenere le dimensioni dei moduli elettronici

disponendo i componenti in modo assiale, tra due schede a circuito stampato.

Questo metodo di fabbricazione dei circuiti elettronici nacque per impieghi

militari e nel settore delle telecomunicazioni; a causa del costo elevato,

solamente pochi produttori di computer (ad es. CDC, Ferranti) lo impiegarono

estensivamente nelle proprie macchine. Cadde definitivamente in disuso con

l'affermarsi delle tecnologie di montaggio superficiale (SMT).

Vedi: http://research.microsoft.com/en-us/um/people/gbell/craytalk/sld034.htm;

http://www.nixiebunny.com/cdc6600/index.html.

Anche: http://infolab.stanford.edu/pub/voy/museum/pictures/display/0-1-logic-timeline.htm.

Anche: http://pages.sbcglobal.net/couperusj/Memory.html;

http://homepages.nildram.co.uk/~wylie/ICs/package.htm.

Anche (sull'evoluzione

delle tecnologie di packaging): http://www.svec.org/files/SVEC%20Journal%20Volume%201.pdf.

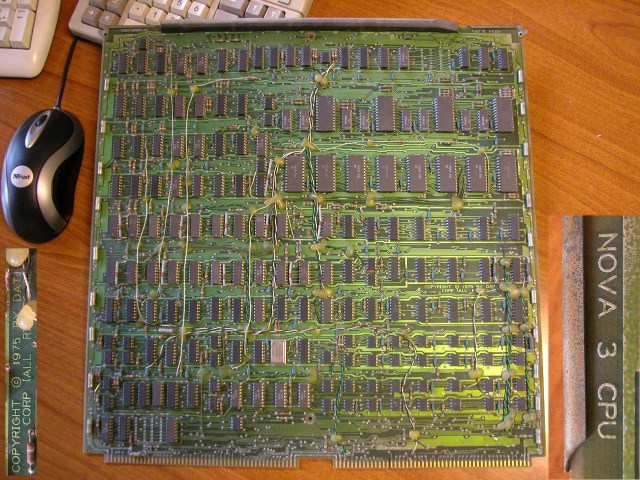

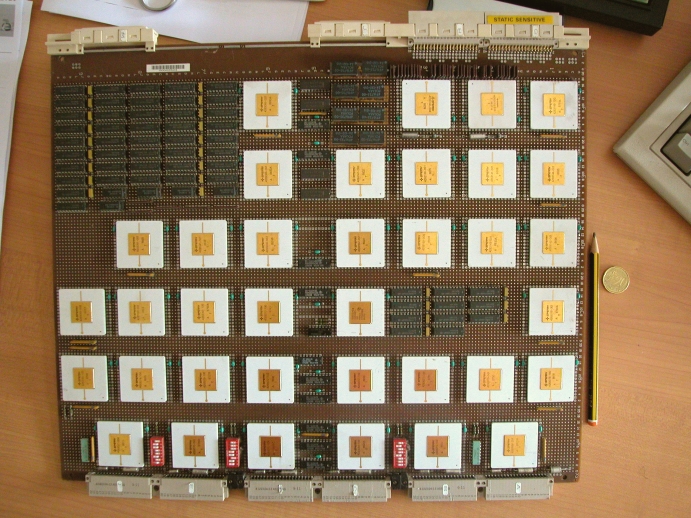

Moduli logici della CPU

di un calcolatore Control Data Corporation (CDC) 3300 (1965). La famiglia

3000, prodotta da CDC fino all'inizio degli anni Settanta, derivava dai

precedenti calcolatori della serie 1600 (in particolare dal 1604). Si trattava

di computer con architettura a 48 (fascia alta) oppure 24 bit (fascia bassa),

pensati in origine per applicazioni tecnico/scientifiche e, rispettivamente,

commerciali.

Vedi: http://www.cs.umass.edu/~verts/cmpsci201/spr_2004/Lecture_33_2004-04-30_CDC-3300_and_6000.pdf.

Anche: http://www.bitsavers.org/pdf/cdc/3x00/.

Anche: http://archive.computerhistory.org/resources/text/CDC/CDC.3000.1964.102646247.pdf.

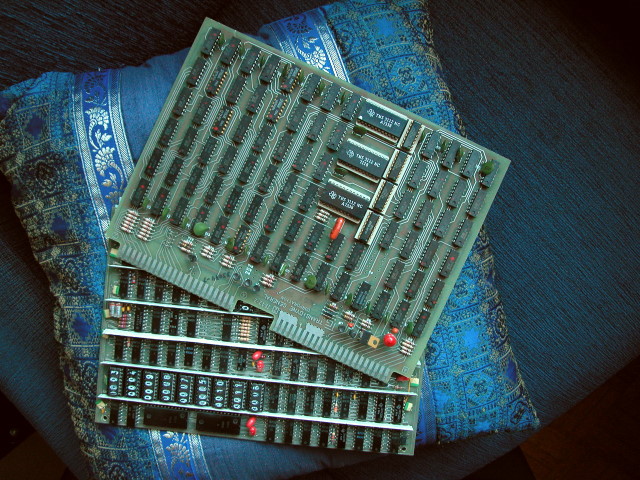

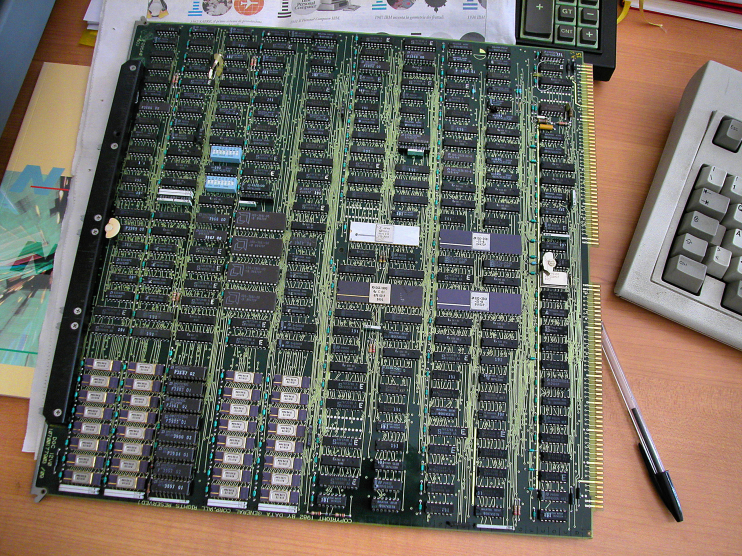

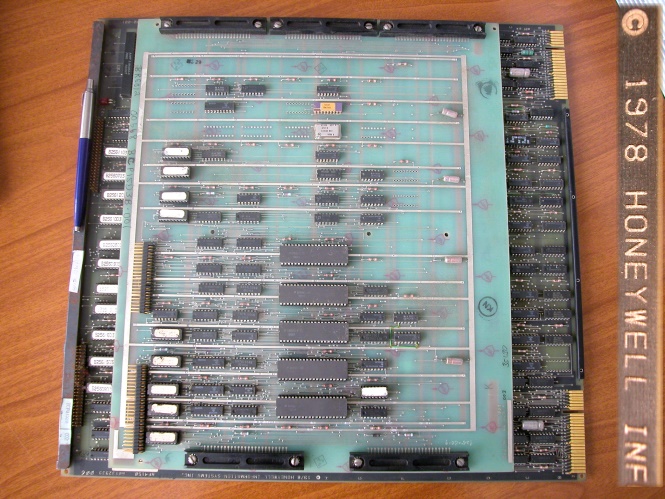

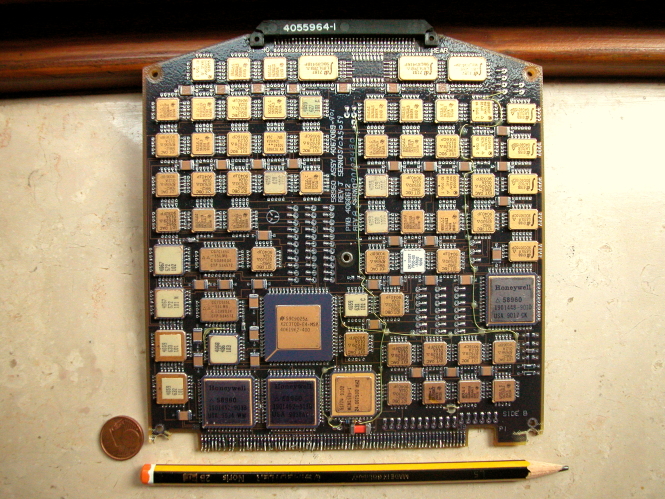

Schede della CPU di un

minicomputer Honeywell della Serie 200 o H-200 (questi

esemplari sono del 1970). Probabilmente appartengono ad un Model 110 del 1968.

La Serie 200, introdotta nel 1963 per contrastare il successo dll'IBM 1401, è

una famiglia di minicomputer per applicazioni commerciali sviluppata e prodotta

da Honeywell ed in seguito da NEC (col nome NEAC-2200) fino al 1974, quando

venne introdotta la più moderna Serie 60 Level 64 che includeva un emulatore

dell'architettura H-200.

Vedi: http://www.feb-patrimoine.com/PROJET/honeywell200/h-200.htm

(in francese).

Sulla concorrenza IBM

1401 contro H-200: http://ed-thelen.org/1401Project/1401-Competition.html.

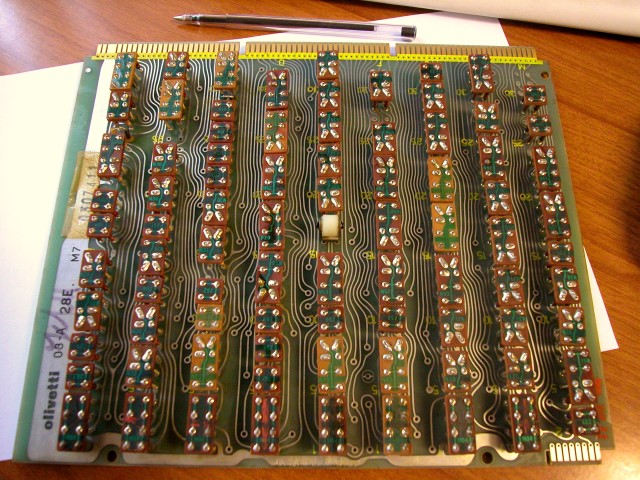

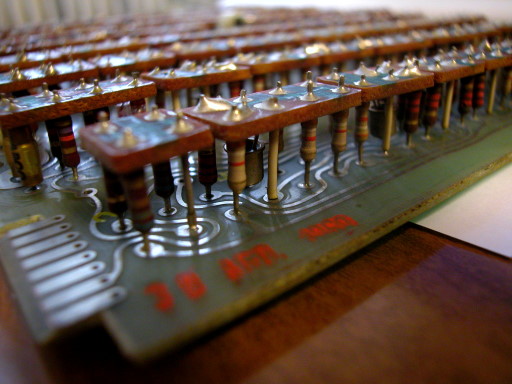

Scheda Olivetti (1969)

con micromoduli "cordwood" a transistor, simile nell’organizzazione a quelle utilizzate

nella Programma 101 del 1963 (vedi ad es.: http://www.classiccmp.org/dunfield/calc/index.htm).

La logica è di tipo RTL (Resistor-Transistor Logic). Le schede sono costruite

in modo tale da contenere il più possibile le dimensioni dei sistema. Questa

scheda appartiene ad una Olivetti Logos 328 (1968, vedi),

prima calcolatrice elettronica da tavolo

prodotta dalla casa di Ivrea (sostanzialmente una Programma 101... non

programmabile). Vedi: http://www.storiaolivetti.it/slideshow.asp?idPercorso=578.

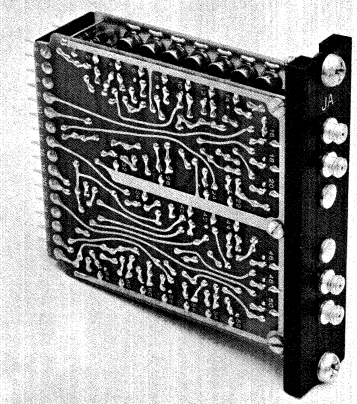

Vista laterale dei

moduli RTL.

Vedi: http://www.oldcalculatormuseum.com/c-programma101.html;

http://cicloinf.dimi.uniud.it/mostra/Pagina13.html;

http://www.silab.it/frox/p101/.

Anche: http://www.costanzoscuole.it/studenti/index.php?option=com_content&task=view&id=15&Itemid=30

(notevole!)

Scheda Beckman del 1968

contenente logica RTL discreta.

Scheda di calcolatore UNIVAC (modello

1107...?) del 1967 contenente 7 transistor e vari componenti passivi

(resistori e condensatori).

Altro esempio di scheda di calcolatore

a transistor. Anche questa è una scheda UNIVAC ed è stata fabbricata nel 1968.

Probabilmente apparteneva ad una macchina modello 9200.

Vedi: http://www.computermuseum.li/Testpage/UNIVAC9200.htm;

http://www.cs.unc.edu/~yakowenk/classiccmp/univac/.

Vedi anche: http://www.technikum29.de/en/computer/univac9400.shtm;

http://www.tecnoteca.it/museo/13.

Vedi anche: http://archive.computerhistory.org/resources/text/Remington_Rand/SperryRand.UNIVAC9000.1967.102646204.pdf.

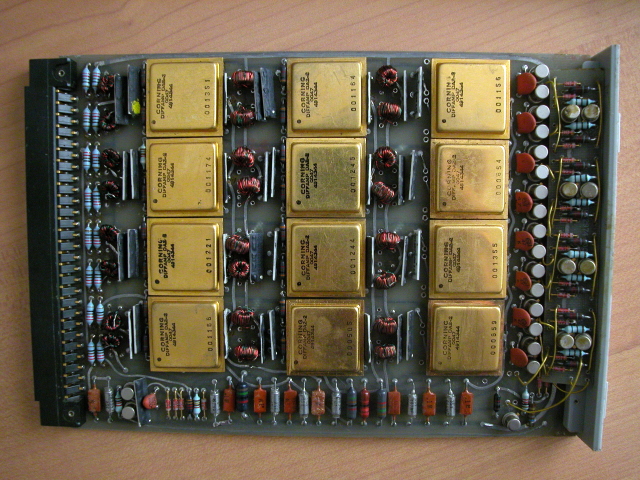

Scheda UNIVAC, appartenente ad un

sistema non identificato (9200?), contenente 12 amplificatori differenziali Corning

(circa 1967) realizzati come circuiti ibridi thick-film.

Vedi: http://people.cs.und.edu/~rmarsh/CLASS/CS451/HANDOUTS/os-unisys.pdf.

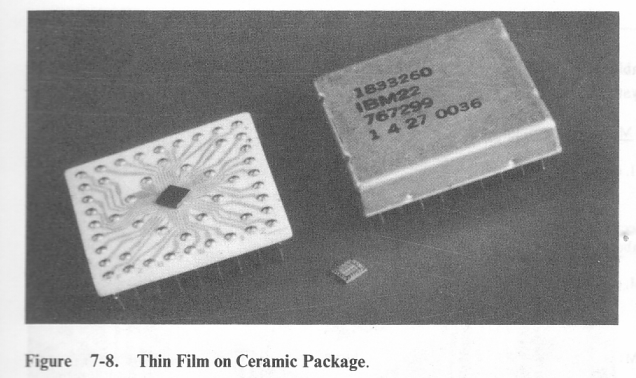

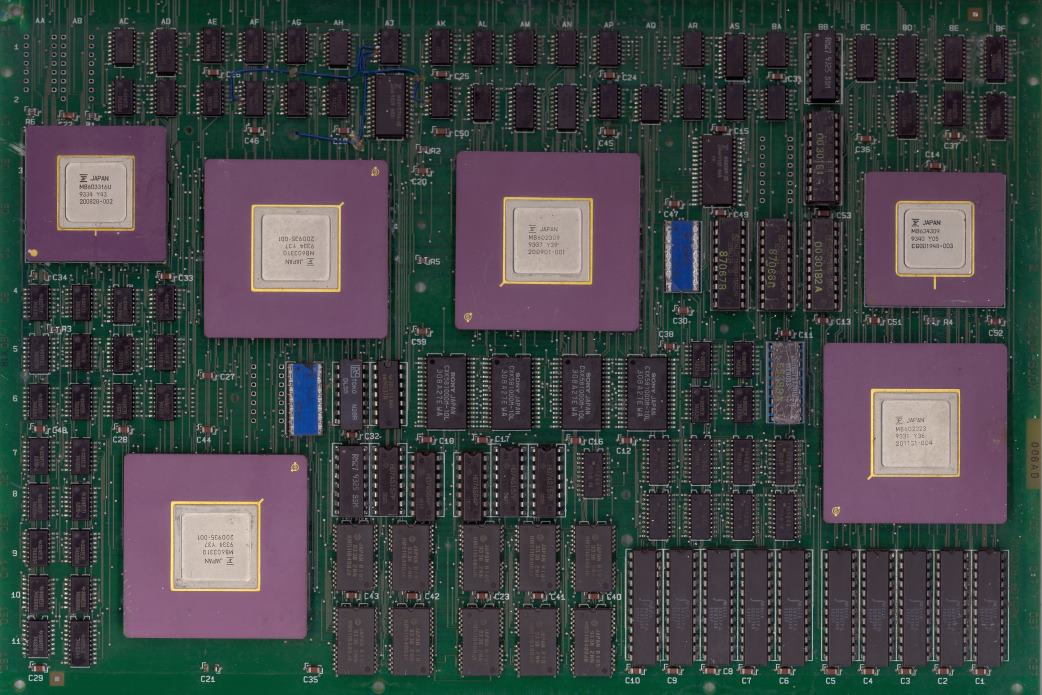

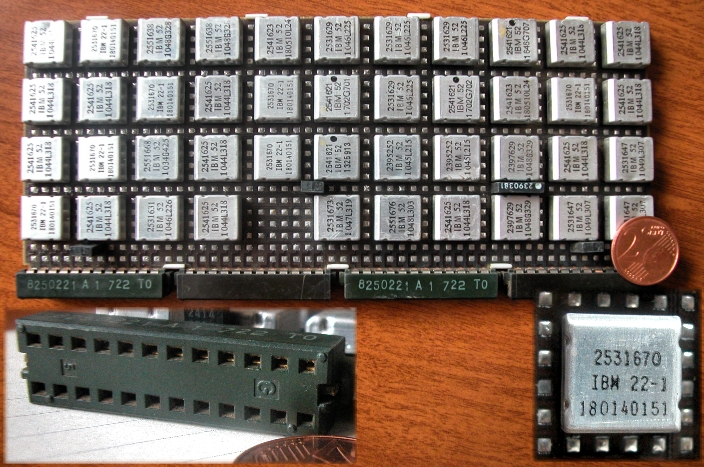

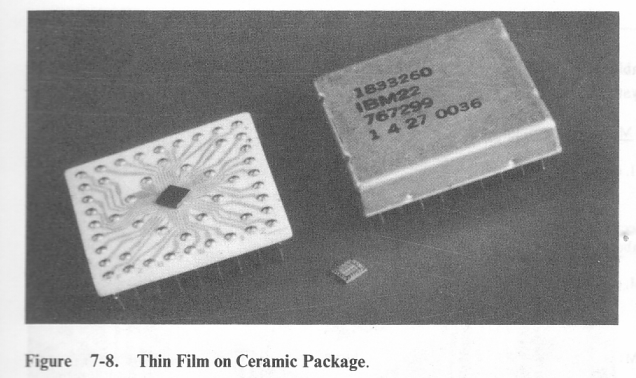

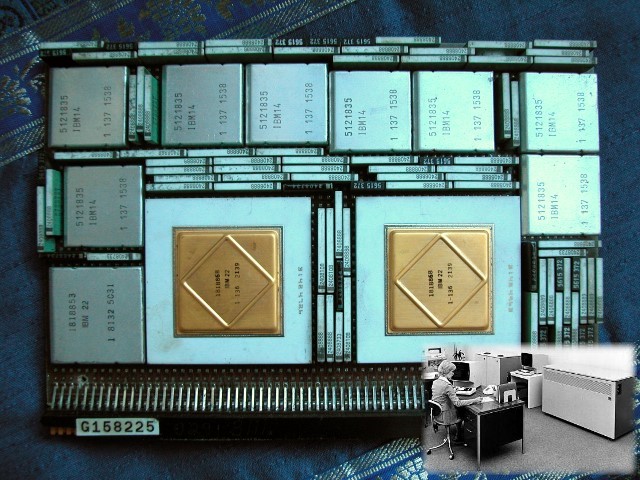

La tecnologia SLT (Solid Logic

Technology) di IBM, introdotta nel 1964 col calcolatore System/360 (vedi), è basata

sull’impiego di circuiti ibridi a film spesso (thick film) contenuti in

caratteristici contenitori di alluminio (metal can) delle dimensioni di circa 1

x 1 cm, rimasti poi in uso per decenni ed adattati a contenere anche veri e

propri circuiti integrati. SLT, una tecnologia rivoluzionaria al momento della

sua introduzione, è stata il primo e più diffuso processo industriale

automatizzato di fabbricazione di circuiti elettronici "microminiaturizzati",

il passo precedente ai circuiti integrati monolitici. I moduli SLT sono formati

da una base (substrato) di ceramica sul quale venivano realizzate le connessioni

circuitali e fissati i componenti (diodi e transistor). I resistori erano

realizzati invece con procedimento serigrafico (silkscreen, vedi).

Più moduli erano infine saldati su piccole schede multistrato (vedi sotto).

L’utilizzo della tecnologia SLT, che offriva notevoli vantaggi in termini di

affidabilità, dimensioni e velocità operativa, è stato una delle ragioni del

successo del System/360 e di altri calcolatori che l’hanno impiegata (come

l’IBM 1130). L’SLT si è evoluta alla fine degli anni Sessanta nella

tecnologia Solid Logic Dense che permetteva un più elevato livello di

integrazione e successivamente nella MST (Monolithic System Technology),

introdotta nel 1969 ed utilizzata a partire dal 1970 con l’IBM System/370, basata su circuiti integrati monolitici. Il

formato delle schede SLT è rimasto in uso per anni, fino alla metà degli anni

Ottanta, ed è stato impiegato in moltissime macchine IBM. Queste schede sono

dotate di caratteristici connettori "femmina" che le collegano al

backplane il quale è specularmente caratterizzati dalla presenza di più file

di connettori "maschio" (il contrario di quanto accade normalmente:

IBM scelse questa soluzione perché garantiva maggiore affidabilità nelle

connessioni tra schede e backplane).

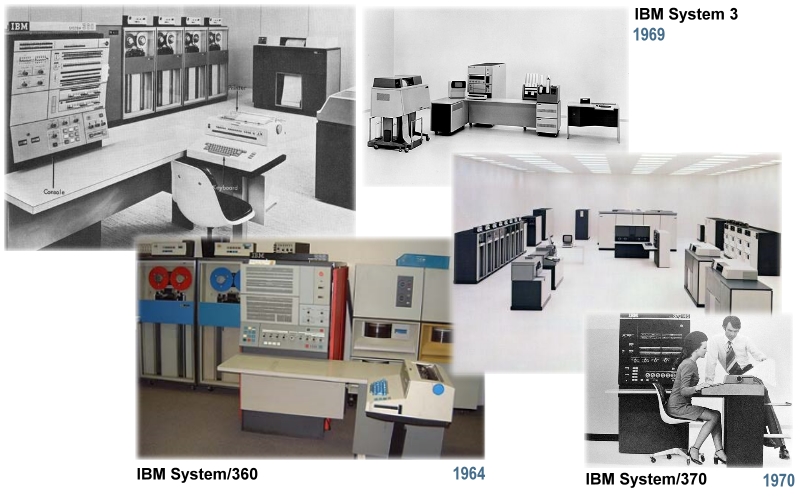

Foto d'epoca per alcuni modelli di

calcolatori IBM System/360, System 3 e System/370.

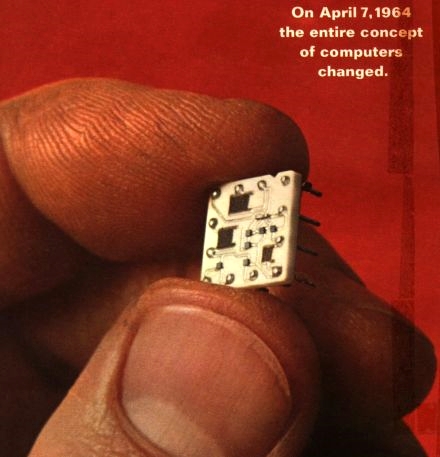

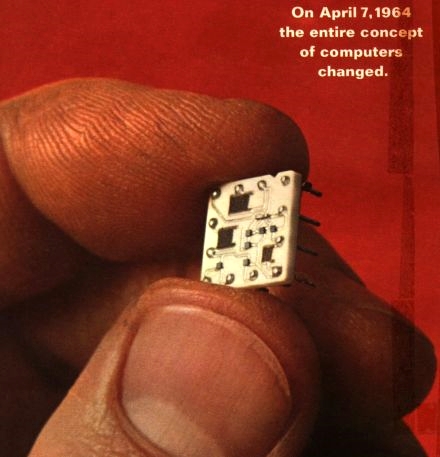

Un modulo SLT in un'immagine tratta da

una brochure commerciale IBM dedicata all'introduzione del System/360 nel

1964. IBM puntò molto, a livello di marketing, sull'importanza dell'innovazione

tecnologica determinata dall'introduzione dei circuiti integrati (ibridi, in

questo caso) in un computer a larga diffusione come l'S/360.

Vedi: http://www-03.ibm.com/ibm/history/exhibits/vintage/vintage_4506VV3081.html;

http://www.flipchips.com/tutorial06.html.

Vedi (IBM System/360): http://infolab.stanford.edu/pub/voy/museum/pictures/display/3-1.htm;

http://homepages.kcbbs.gen.nz/nbree/saga.html.

Anche: http://archive.computerhistory.org/resources/text/IBM/ibm_%20360_revolution_story_102634496.pdf.

Sul System/360: http://www.punch-card.co.uk/mainframe.htm;

http://www.columbia.edu/acis/history/generations.html.

Sempre sull'IBM S/360: http://archive.computerhistory.org/resources/text/IBM/IBM.System_360.1964.102646088.pdf.

Sull'evoluzione dei

calcolatori IBM: http://archive.computerhistory.org/resources/text/IBM/IBM.various.1976.102646158.pdf.

Vedi (IBM 1130): http://ibm1130.org/hw/cpu.

Articolo originale IBM:

http://www.research.ibm.com/journal/rd/082/ibmrd0802D.pdf.

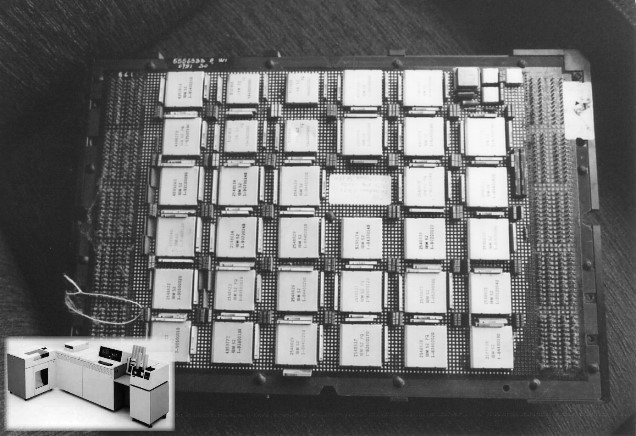

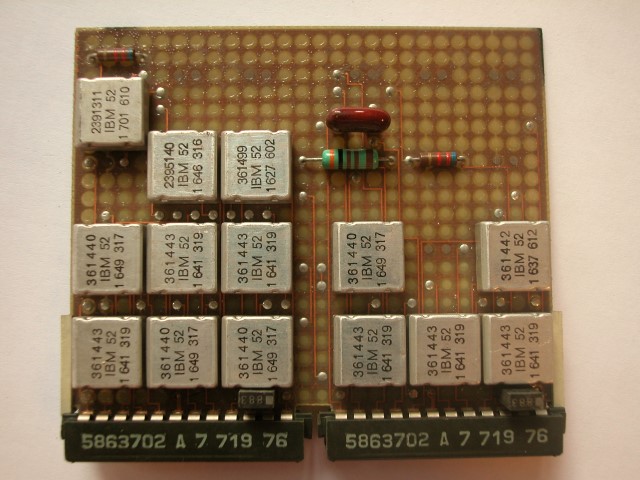

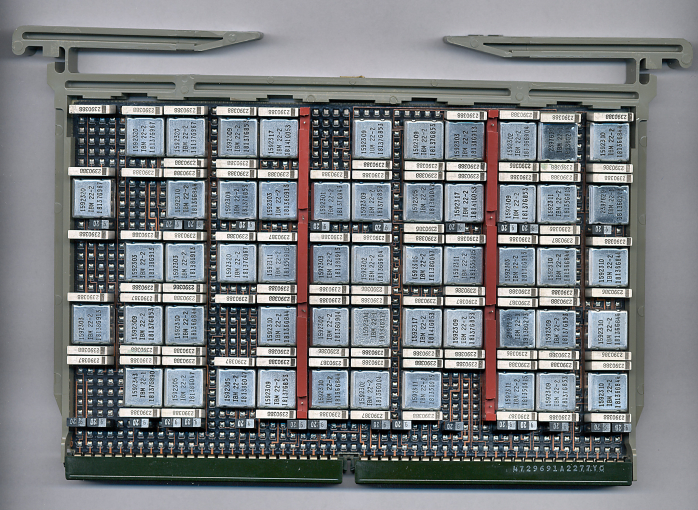

Scheda IBM con circuiti SLT, primi

anni Settanta. Le schede

di questo tipo, altamente modulari, sono state fabbricate in più formati

standard (questa è una "double height" o scheda a doppia altezza) ed

a uno o più strati di circuito stampato (fino ad un massimo di due per i

segnali e due per l’alimentazione). Le "piste" (connessioni) di

quest’ultimo passano in mezzo ai punti di saldatura dei piedini dei moduli SLT.

A seconda del formato le schede hanno un numero definito di punti di saldatura

disponibili (546 in questo caso). I moduli SLT possono avere al massimo 16

piedini organizzati in una matrice 4x4 con passo di 125 mil (millesimi di

pollice).

Vedi: http://www.computerhistory.org/semiconductor/timeline/1964-Hybrid.html.

Modulo SLT dall’inusuale formato,

proveniente da un modem IBM.

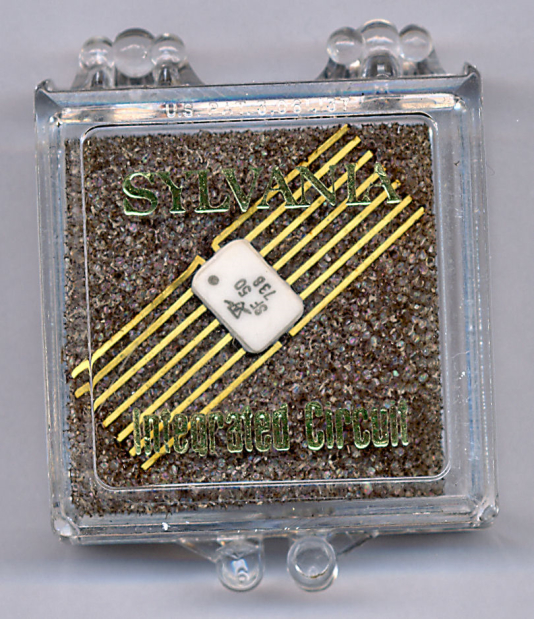

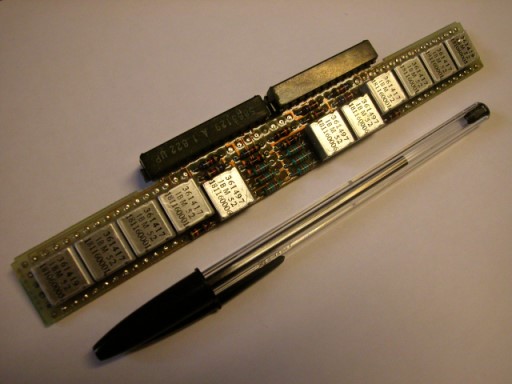

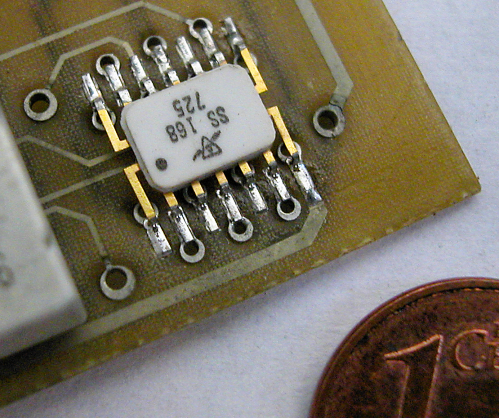

Questa insolita scheda IBM con moduli

SLT (1967) contiene due integrati Sylvania in flat-package (a destra). A che

macchina apparteneva? Non ne ho idea! Notate la non comune marcatura dei moduli

(IBM-YV).

Dettaglio di uno dei due integrati

Sylvania contenuti nella scheda raffigurata sopra. Sulla base di quanto

riportato in questo

interessantissimo sito dedicato ai primi integrati logici, dovrebbe

trattarsi di un membro della famiglia SUHL (Sylvania Universal High-level

Logic), prima famiglia logica TTL di successo (i primi integrati TTL in assoluto

erano stati fabbricati qualche anno prima, nel 1961, dalla Pacific

Semiconductors - poi TRW).

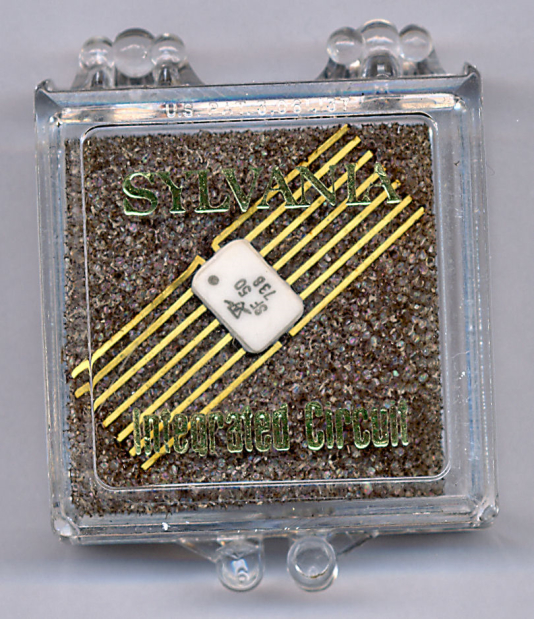

Flip-flop

TTL Sylvania SF50 appartenente alla famiglia SUHL (vedi sopra).

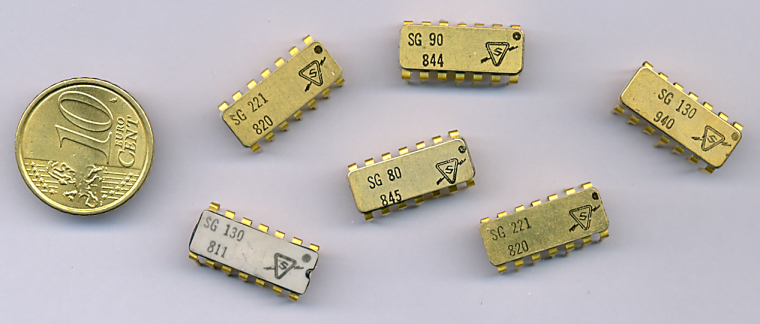

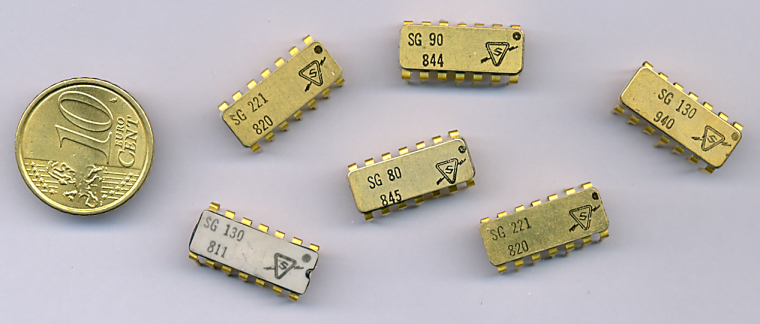

Integrati Sylvania SUHL (Sylvania

Universal High-level Logic) in package CERDIP gold-plated, 1968/9. Vedi questa

pagina.

Struttura di un tipico package IBM

SLT.

Modulo IBM in standard SLT contenente

esclusivamente transistor.

Vedi:

http://ibmcollectables.com/gallery/view_album.php?set_albumName=album128.

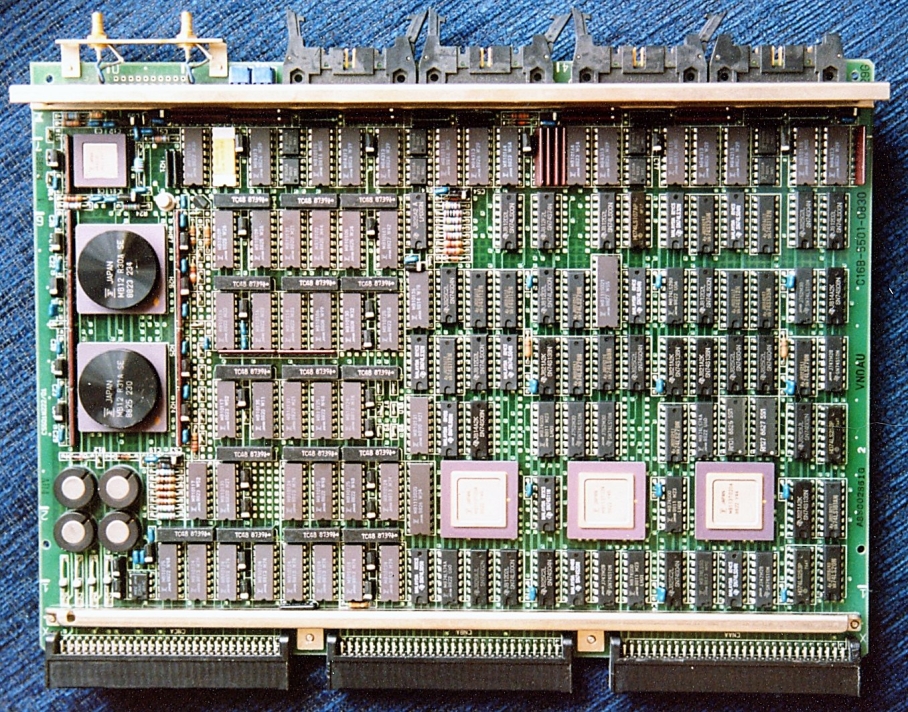

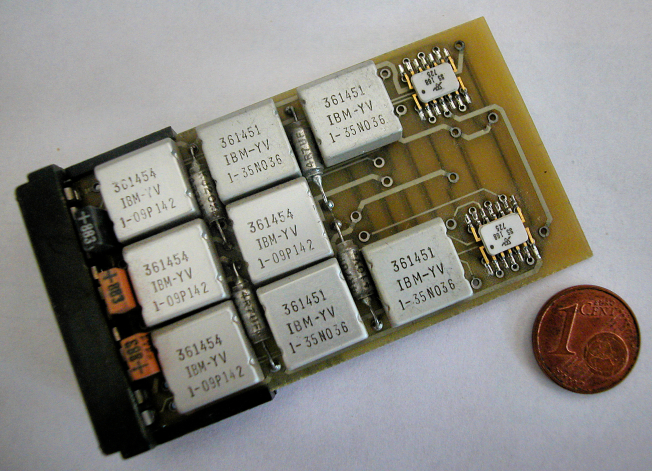

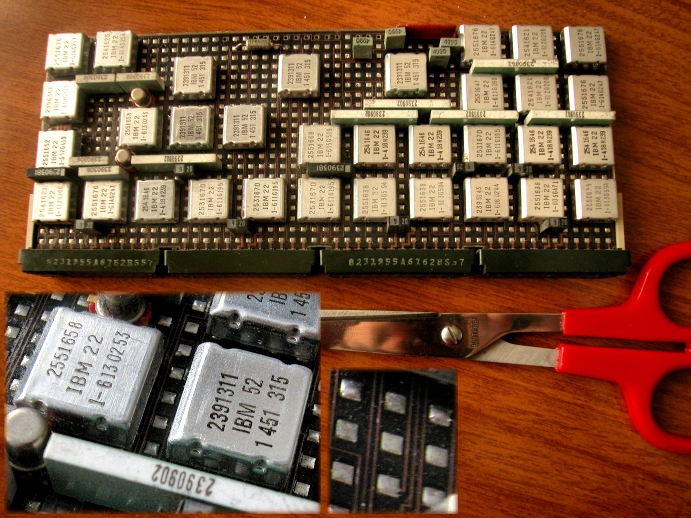

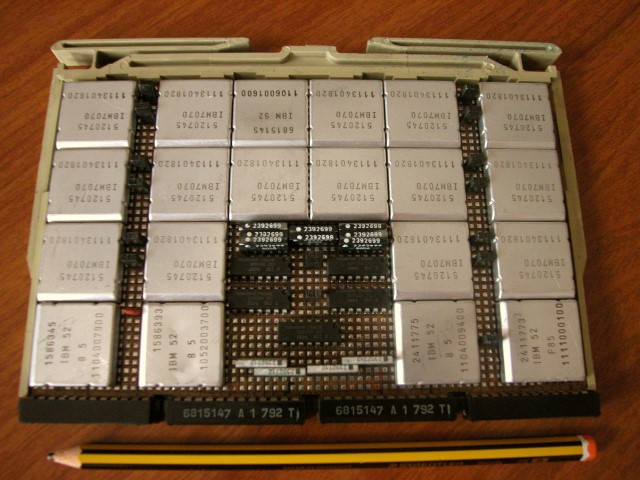

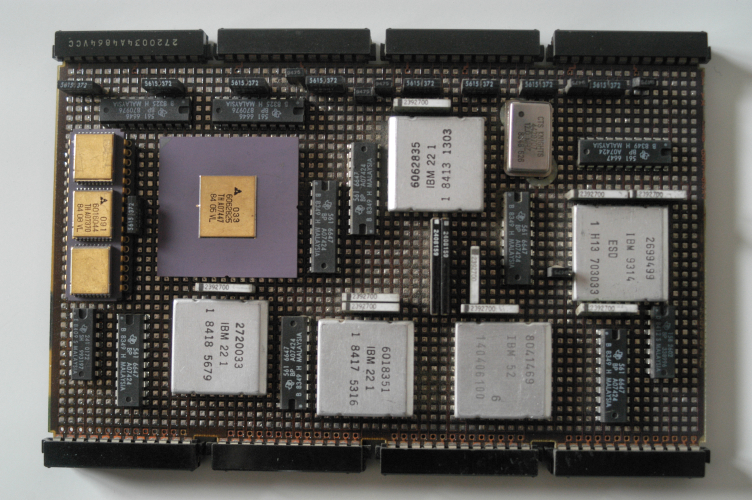

Scheda con moduli MST, da un calcolatore IBM System/3.

La tecnologia MST, introdotta nel 1968 col System/370, impiega package

(contenitori) molto simili a quelli dei moduli SLD, a loro volta evoluzione dei

precedenti SLT: quadrati con lato di 0,5 pollici, 16 pin (distanziati fra loro

di 0,8 pollici - i moduli SLT avevano invece solo 12 pin). I chip sono montati

rovesciati (face-down o flip-chip) su un substrato ceramico sul quale sono

realizzate le connessioni con i piedini. Il tutto è ricoperto da gel protettivo

a base siliconica (vedi: http://ibmcollectables.com/gallery/whittemore-1/logic_chips).

L’unione tra chip e substrato è realizzata col metodo C4 (Controlled-Collapse

Chip Connection). I moduli MST utilizzano un connettore di backplane femmina

anziché maschio, simile a quello delle schede SLT - dettaglio in basso a

sinistra. Le prime schede MST erano a singolo strato (single-layer); quelle

multilayer furono introdotte successivamente negli anni Settanta. In queste

schede tra un punto di saldatura e quello adiacente possono transitare fino a 3

piste di circuito stampato per ciascuno strato (vedi sotto).

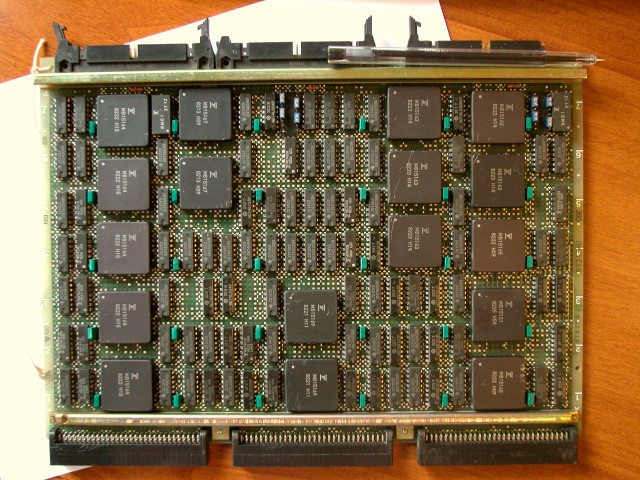

Scheda con moduli MST facente parte della CPU di un calcolatore IBM System/370

Model 125 (1972, la scheda è dei primi anni Settanta). In basso a sinistra

un dettaglio dei moduli, immediatamente a destra un dettaglio delle piste del

circuito stampato che passano tra i punti di saldatura dei piedini.

La prima generazione di moduli MST (MST-1), che contengono integrati logici

CSEF (una forma di ECL, la sigla sta per "Current Switch Emitter Follower"),

è stata anche utilizzata nel System/3 (1969, vedi: http://www.corestore.org/3.htm)

ed in parecchie periferiche IBM degli anni Settanta, nonché nei mainframe IBM

3033. Si tenga presente che prima dell'affermarsi degli integrati CMOS furono

sviluppate parecchie famiglie logiche bipolari basate su altrettante varianti

dell'ECL e della logica TTL. La famiglia System/3 è in effetti fabbricata

impiegando un mix di tecnologie, in parte SLD (Solid Logic Dense, soprattutto

nella sezione di I/O) ed in parte MST. Quest'ultima è stata oggetto nel corso

degli anni di una serie di revisioni ed ammodernamenti noti (MST-2, MST-4…)

che hanno riguardato tanto il packaging, ad esempio con l'introduzione di moduli

più grandi, quanto i circuiti integrati veri e propri, passati alla logica TTL.

Il formato originario dei moduli MST è tuttavia rimasto in uso per più di

vent'anni, fino alla metà degli anni Novanta.

Vedi: http://www.bitsavers.org/pdf/ibm/logic/MST-2_Module_Data_Apr74.pdf.

Anche: http://www.bitsavers.org/pdf/ibm/logic/SY22-2798-2_LogicBlocks_AutomatedLogicDiagrams_SLT,SLD,ASLT,MST_TO_Oct71.pdf.

Anche: http://www.cbi.umn.edu/hostedpublications/pdf/IBMRochesterHistory.pdf.

Anche: http://www.ibmsystem3.nl/hist.html.

Logica IBM CSEF: http://portal.acm.org/citation.cfm?id=1663057&dl=GUIDE&coll=GUIDE&CFID=73308600&CFTOKEN=46699233.

Anche: http://www.cs.clemson.edu/~mark/acs_technical.html

(interessante).

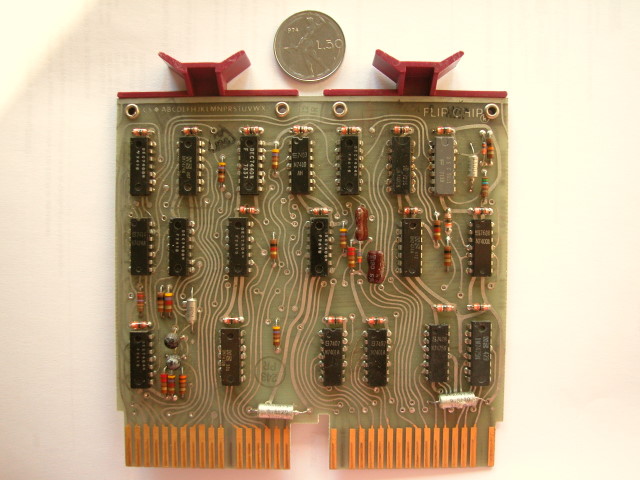

Durante gli anni Sessanta si sviluppa

e si afferma la tecnologia dei circuiti integrati monolitici (il circuito integrato era

stato inventato nel 1958). Dopo un periodo di incertezza circa la sua reale

affidabilità, alla fine del decennio tutti i principali produttori

di calcolatori utilizzano questa nuova tecnologia, che consente un notevolissimo

risparmio di dimensioni e maggiore velocità di

elaborazione. I calcolatori a circuiti integrati sono detti

comunemente computer "di terza

generazione". Qui un modulo DEC FlipChip (del 1973), del tipo di quelli

usati nei minicalcolatori PDP. La tecnologia FlipChip (da non confondersi con

l’omonima tecnica di montaggio dei componenti a semiconduttore) venne

introdotta nel 1964, esattamente come l’SLT di IBM. Essa deve il nome al fatto

che nelle prime schede di questo tipo erano effettivamente montati diodi e

transistor realizzati con la tecnica di packaging "flip chip" (vedi).

Il termine divenne quindi un marchio registrato di DEC e rimase in uso per anni.

Scheda Burroughs del 1969 con

transistor ed integrati Philco (vedi dettaglio). Apparteneva ad un calcolatore L5000.

Scheda di calcolatore elettronico del

1970 (vedi dettaglio) con integrati SSI di Texas Instruments, Fairchild e Sylvania

e componenti passivi. Faceva

probabilmente parte di un calcolatore UNIVAC. Sylvania introdusse nel 1963 la

prima famiglia logica TTL commerciale di successo, la SUHL (Sylvania Universal

High-level Logic), fabbricata anche come second-source da Raytheon. Storicamente

i primi integrati logici TTL furono prodotti nel 1961 da Pacific Semiconductors,

diventata in seguito TRW.

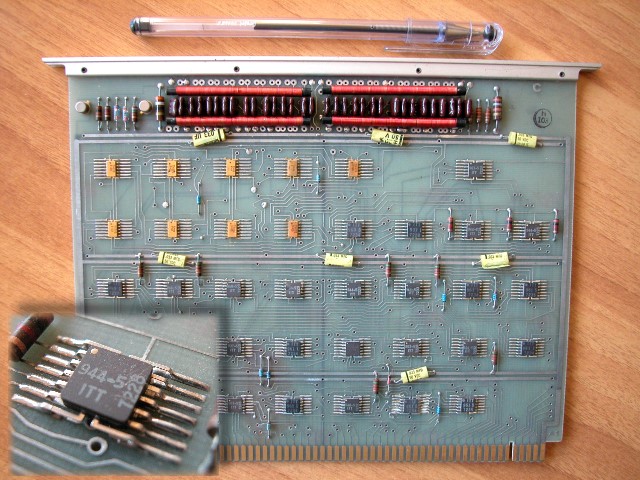

Scheda di calcolatore Honeywell

(probabilmente un minicomputer 316, vedi)

del 1972 con

circuiti integrati logici di tipo DTL (Diode-Transistor Logic) a bassa scala di integrazione (SSI)

fabbricati da ITT, equivalenti alla serie 930 di Fairchild. Gli anni Sessanta vedono la nascita delle prime

famiglie di circuiti integrati logici standardizzate, tra le quali si afferma in

modo particolare la "Serie 74" di Texas Instruments, una vastissima famiglia di circuiti

TTL realizzati con tecnologia bipolare.

Scheda logica di una calcolatrice

elettronica Olivetti Logos 270. Questa macchina, presentata nel 1970, fu

la prima "vera" calcolatrice elettronica Olivetti: il modello

precedente, cioè la Logos 328 (1968), era in realtà una versione non

programmabile del calcolatore da tavolo Programma 101 introdotto nel 1965. Della

Logos 328 il modello 270 mantiene la memoria a linea di ritardo magnetostrittiva

(delay-line), qui alloggiata nel contenitore rettangolare di alluminio.

L'elettronica è formata da circa 150 integrati SSI DTL, fabbricati da ITT

(vedi dettaglio), Signetics, Philco e Fairchild - il datecode è del 1969, la

scheda è stata prodotta nel Marzo 1970. L'interno del modello 240, simile ma

meno potente della Logos 270, è descritto dettagliatamente (compreso il

funzionamento della linea di ritardo) qui: http://home.vicnet.net.au/~wolff/calculators/Tech/Logos240/Logos240.htm.

Contrariamente all'antenata Logos 328, la 270 è interamente realizzata con

circuiti integrati. L'integrato ITT nel dettaglio (MIC930) è una doppia porta

NAND a quattro ingressi, elemento di base della famiglia DTL introdotta nel

1968.

Vedi (serie ITT

MIC930): http://www.datasheetarchive.com/pdf-datasheets/Databooks-4/Book-33355.html.

Le prime

famiglie logiche

La prima famiglia logica introdotta

sul mercato è stata, nel 1962, la serie SE100 di Signetics (DTL). A questa ha

fatto seguito l’anno successivo la "Series 930" di Fairchild. Sempre

nel ’63 è quindi arrivata la prima famiglia TTL, la SUHL (Sylvania’s

Universal High Logic) di Sylvania, seguita nel 1964 dalla SN5400 di Texas

Instruments (anch’essa TTL) e quindi dalla famosa SN74xx, sempre di TI, nel

1966 (prima famiglia logica TTL contenuta in package plastici a basso costo).

Nel 1968, con il progredire delle tecniche litografiche impiegate nella

realizzazione degli integrati logici, comparvero i primi circuiti TTL MSI (con

più di 100 gate logici per chip), in particolare le serie 9300 di Fairchild ed

8200 di Signetics. Ricordiamo che la logica TTL era stata brevettata ancora nel

1961 da James Buie della Pacific Semiconductor Co.

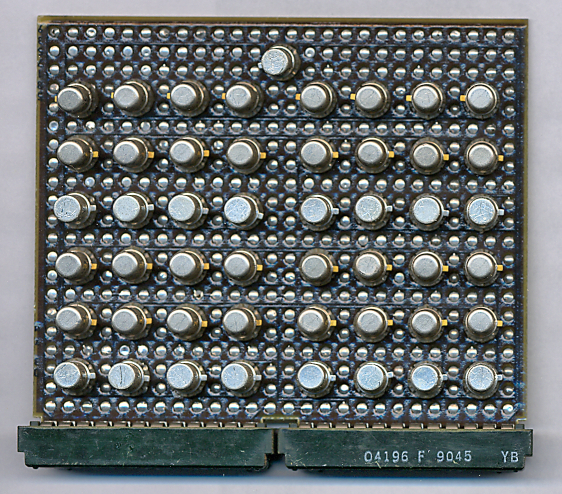

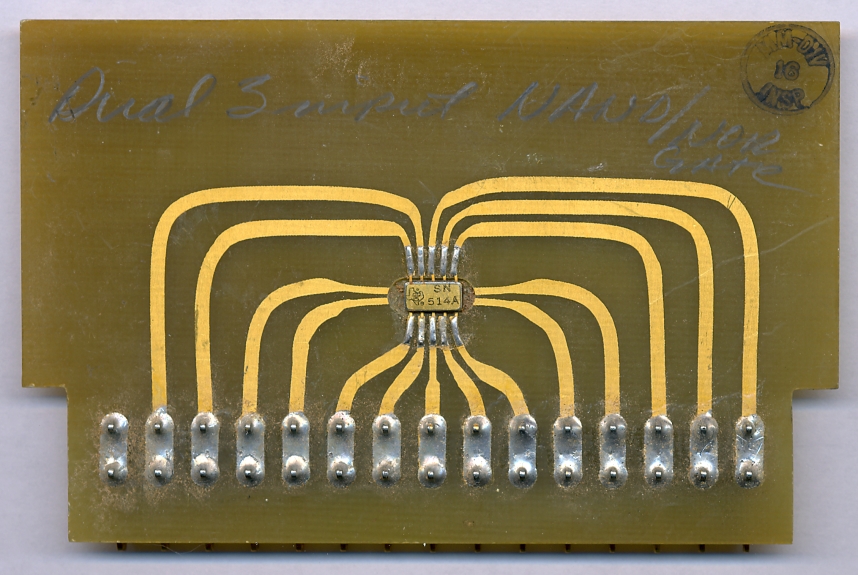

Integrato Texas Instruments SN514A

in package flat-pack ceramico saldato su scheda per test (1961). La

serie SN51x di Texas Instruments, introdotta nel 1960, è spesso riconosciuta

come la prima famiglia di integrati logici commercialmente disponibile.

La stessa TI aveva presentato qualche mese prima, nel Marzo 1960, il primo

circuito integrato logico commerciale, l'SN502 (prodotto solamente per un breve

periodo di tempo, e con tecnologia mesa anziché planare -sviluppata dalla

Fairchild- come i successivi); tale circostanza è citata nel libro Introduction

to Integrated Semicondutor Circuits di Khambata (McGraw-Hill, 1963): "[...]

in 1960, Texas Instruments announced the introduction of the earliest product

line of integrated logic circuits. TI's trade name is 'Solid Circuits' for this

line. This family, called the series 51, utilized the modified DCTL circuit [...]".

La maggior parte degli integrati SN51x sono stati destinati ad applicazioni

militari ed aerospaziali; in particolare la NASA è stata in pratica l’unico

utilizzatore su larga scala delle prime serie, quelle cioè in package ceramico.

Due membri di questa famiglia, l’SN510 e l’SN514, sono stati i primi

circuiti integrati impiegati in un veicolo spaziale, la sonda Interplanetary Monitoring

Probe (IMP) lanciata nel Novembre del 1963. Gli SN51x sono circuiti DCTL (Direct-Coupled

Transistor Logic, vedi),

un tipo di logica inizialmente designata con la sigla RCTL (Resistor-Capacitor

Transistor Logic), a motivo del fatto che ai resistori collegati alle basi dei

transistor sono affiancati altrettanti condensatori, per aumentare la velocità

di commutazione del circuito. La sigla "SN" sta per "Semiconductor

Network" (letteralmente, rete di semiconduttori), termine utilizzato all’epoca

da Texas Instruments per designare i propri circuiti integrati. L'SN514 è una

doppia porta NAND/NOR a 3 ingressi (vedi).

"Engineer

Bob Cook designed Series 51 DCTL, Texas Instruments' first planar IC family, to

meet a low-power specification for the Optical Aspect Computer on NASA’s

Interplanetary Monitoring Probe (IMP). Using the SN510 and SN514 as binary

counters, flip-flops, and inhibiting circuits, the IMP satellite carried the

first ICs into orbit in 1963. In 1962 TI won a contract from the Autonetics

Division of North American Aviation to design 22 custom circuits for the

Minuteman II missile guidance system. Clevite and Westinghouse also developed

circuits for the Minuteman

project, which by 1965 overtook NASA's Apollo procurement as the largest single

consumer of ICs." (vedi questa

pagina).

"Since TI

and Fairchild were the co-inventors of the IC, one might expect that they would

release the first commercial devices, and in fact this was so. In March, 1960,

Texas Instruments announced the introduction of the earliest product line of

integrated logic circuits. TI's trade name is Solid Circuits

for this line. This family, called the series 51, utilized the modified

DCTL circuit and the SN510 and SN514, were the first integrated circuits to

orbit the Earth, aboard the IMP satellite, launched by the US on November 27,

1963 (see the nearby photo). Fairchild's prototype chips were announced in

November 1960, and the company had introduced its first commercial integrated

circuit, the same device as Dummer's a decade ago, a flip-flop (the basic

storage element in computer logic), at an industry convention in New York in

March 1961." (vedi questa

pagina).

Vedi: http://www.decadecounter.com/vta/articleview.php?item=741.

Anche: http://smithsonianchips.si.edu/texas/t_340-1.htm.

Anche: http://history-computer.com/ModernComputer/Basis/IC.html.

Anche: http://www.vintchip.com/flatpack.html

(sito molto interessante).

Anche: http://www.vintchip.com/FLATPACK/DATA/51seriesspace.pdf

(impiego della serie SN51x nelle sonde IMP).

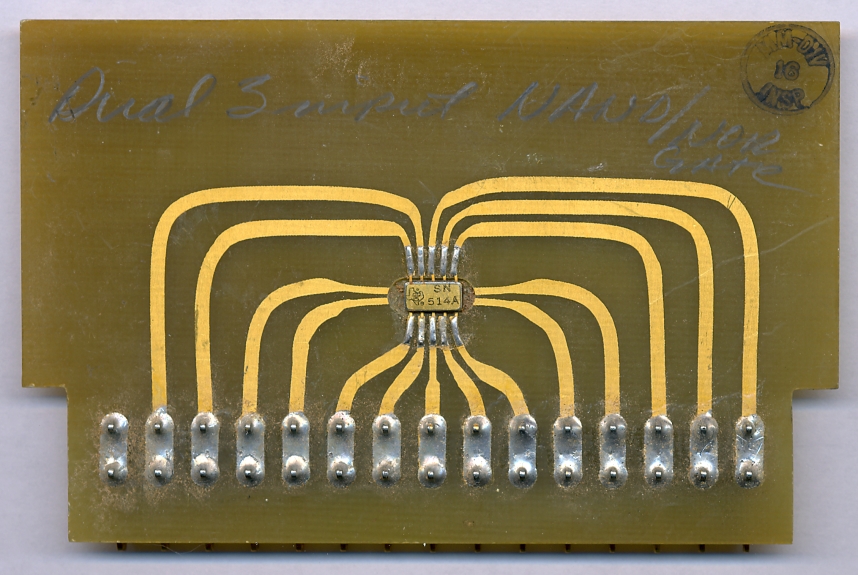

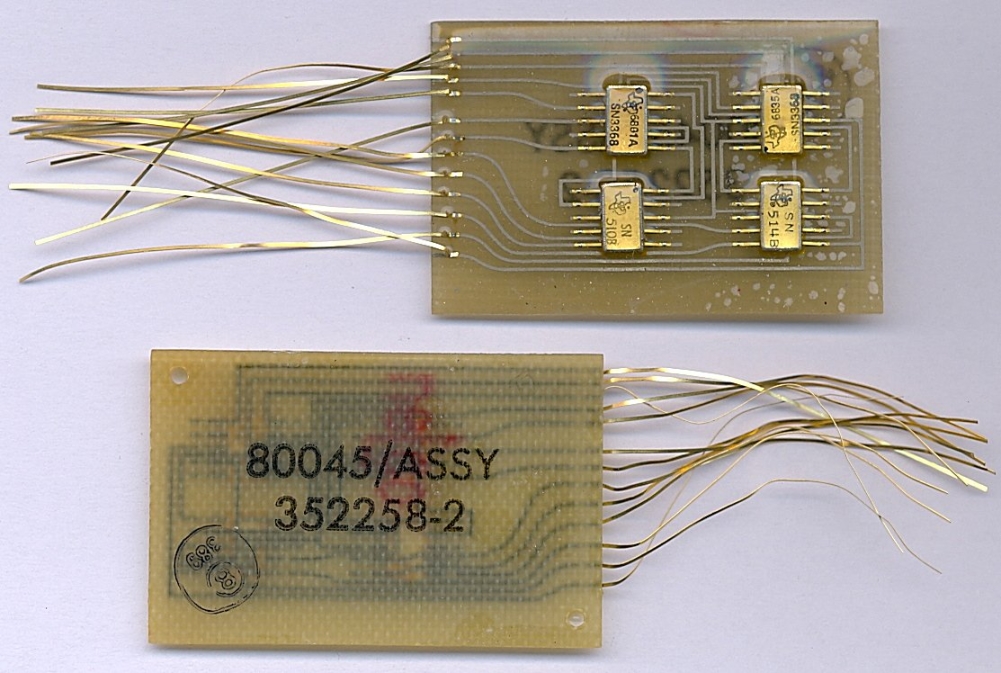

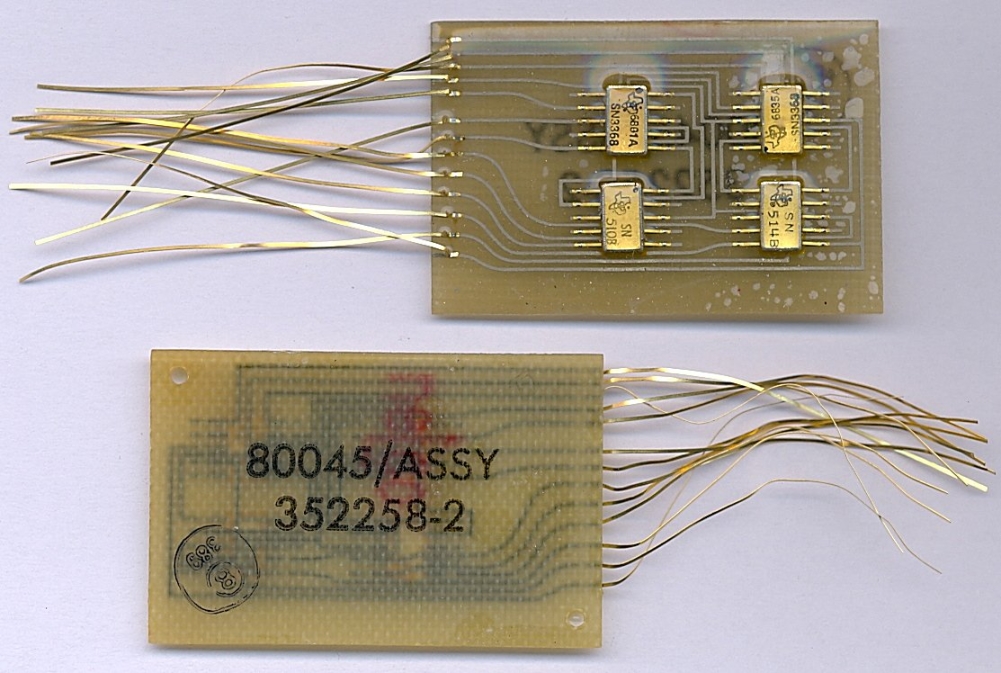

Coppia di moduli (1968) con integrati logici

Texas Instruments della Serie 51 e della serie SN33 "Minuteman

Logic", così chiamata perché impiegata prevalentemente in impieghi

militari come ad esempio l'elettronica di governo dei missili balistici a largo

raggio Minuteman.

Esempio di integrato logico TTL a

bassa integrazione (SSI): un SN7401 fabbricato da Texas Instruments nel

1967, in package small-flat per impieghi militari (qui nel suo contenitore

originale). Il 7401, uno dei più diffusi componenti della Serie 74, contiene

quattro porte logiche NAND a due ingressi, con output open-collector. La sigla

"SN" è l'abbreviazione di "Semiconductor Network" (rete di

semiconduttori), termine impiegato da Texas Instruments nei primi anni Sessanta

per indicare i circuiti integrati.

Questo sito: http://homepages.nildram.co.uk/~wylie/ICs/monolith.htm

illustra, in ordine cronologico, molti esempi di circuiti integrati fabbricati

negli anni Sessanta, tra cui un SN7401 identico a quello raffigurato qui sopra.

Sullo stesso argomento si può anche vedere questo sito: http://www.cs.ubc.ca/~hilpert/eec/.

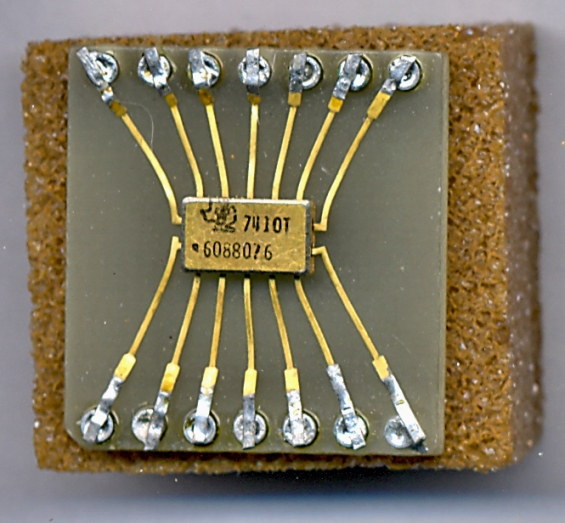

Circuito integrato TTL

della Serie 74 (questo è una tripla porta NAND a tre ingressi, 7410) in package

small-flat fabbricato nel 1966 da Texas Instruments. Il modulo era probabilmente

utilizzato per la prova delle caratteristiche dell'integrato.

Principali

tappe nello sviluppo della tecnologia dei semiconduttori e dei circuiti

integrati

1940:

scoperta, nel campo dei semiconduttori, della giunzione p-n.

1941:

messa a punto delle tecniche per produrre monocristalli di Silicio di elavata

purezza, indispensabili nella fabbricazione di transistor.

1947:

invenzione del transistor a punte di

contatto (J. Bardeen e W. Brattain).

1948:

sviluppo teorico del transistor a giunzione p-n-p (W. Shockley, Bell Labs).

1951:

fabbricazione del primo transistor a

giunzione al n-p-n (G. Teal e M. Sparks). Il transistor a giunzione

è una forma di transistor molto più affidabile e facile da produrre

dell'originario tipo a punte di contatto.

1951:

sviluppo del processo di raffinazione a zone (zone-refining) per produrre

Silicio ultra-puro (W. Pfann e H. Theurer).

1952:

inizia lo sviluppo dell'industria dei transistor.

1952:

viene pubblicato per la prima volta il concetto di "circuito

integrato" (W.A. Dummer, "Solid block with layers of insulating

materials", 7 Maggio 1952).

1953:

primo prototipo di calcolatore elettronico a transistor.

1954:

primo transistor commerciale al Silicio (Texas Instruments, 10 Maggio 1954).

1955:

sviluppo dei primi processi di diffusione per la fabbricazione di transistor (C.

Lee e M. Tanenbaum, Bell Labs).

1955:

introduzione della mascheratura con film di ossido di Silicio durante il

processo di diffusione (C. Frosch e L. Derick).

1955:

primo transistor FET commerciale (Field-Effect Transistor, Bell Labs).

1956:

applicazione delle tecniche di fotolitografia ai processi di mascheratura e

diffusione (J. Andrus e W. Bond).

1958:

primo prototipo di circuito integrato

monolitico (J. Kilby, Texas Instruments, 12 Settembre 1958). Qualche

tempo prima, il 24 Luglio 1958, Kilby aveva sviluppato il primo progetto teorico

di circuito integrato. Nel 1959 l'idea venne infine brevettata dalla stessa

Texas Instruments (U.S. Patent 3.138.743 "Miniaturized electronic

circuit"). Per questa invenzione Kilby ricevette il Premio Nobel per la

fisica nel 2000.

1959:

introduzione del processo "planare" per la fabbricazione dei

transistor al Silicio (J. Hoerni, Fairchild). Questo processo è stato applicato

per fabbricare circuiti integrati monolitici, nei quali cioè tutti i componenti

e le relative interconnessioni sono ottenuti nel medesimo "blocco" di

Silicio: il dispositivo di Kilby prevedeva invece interconnessioni mediante fili

sottili di oro o argento, delicati e di difficile realizzazione. Il processo

"planare" è stato perfezionato, sempre nel 1959, da K. Lehòvec della

Sprague Electric. L'idea di utilizzare uno strato sottile di metallo deposto

mediante evaporazione (strato di metallizzazione) per realizzare le

interconnessioni è stata infine sviluppata, anch'essa nel 1959, da R. Noyce

alla Fairchild. Sulle tecnologie dei primi transistor vedi: http://sites.google.com/site/transistorhistory/early-transistor-technologies.

1959:

primo brevetto di circuito integrato monolitico, producibile in grandi

quantità, fabbricato col processo "planare" (R. Noyce, J. Last).

1960:

sviluppo del transistor MOS (J.

Atalla, D. Kahng, Bell Labs).

1960:

sviluppo del processo di deposizione epitassiale

(epitaxial deposition) per la fabbricazione dei

transistor e dei circuiti integrati, un elemento chiave della moderna

tecnologia dei semiconduttori.

1961:

definitiva affermazione dei transistor al Silicio nelle applicazioni ad alta

velocità.

1961:

brevetto della logica TTL (J.

Buie, Pacific Semiconductor).

1961:

primi circuiti integrati logici

commerciali (Texas Instruments, Fairchild).

1961:

primo integrato MOS sperimentale (F. Heiman, S. Hofstein).

1962:

prime applicazioni, nel settore aerospaziale, dei circuiti integrati.

1962:

sviluppo dei circuiti integrati logici ECL (J. Narud, Motorola).

1963:

invenzione della logica CMOS (F.

Wanlass, Fairchild), che ha permesso di ridurre fino a 6 ordini di grandezza il

consumo di energia dei circuiti integrati rispetto ai modelli bipolari e PMOS

(la logica CMOS venne brevettata nel 1967, U.S. Patent 3.356.858 "Low

Stand-By Power Complementary Field-Effect Circuitry").

1963:

introduzione delle prime famiglie logiche standardizzate e del primo

circuito integrato PMOS (RCA).

1963:

primo brevetto di memoria RAM statica a circuito integrato (R. Norman, Fairchild) .

1964:

introduzione su scala industriale dei circuiti integrati ibridi (IBM SLT).

1964:

invenzione della stampante a contatto, utilizzata nella fabbricazione dei

circuiti integrati per l'esposizione dello strato di photoresist.

1964:

primo circuito integrato NMOS commerciale

(R. Norman, General Microelectronics).

1964:

primo circuito integrato analogico (D. Talbert e R. Widlar, Fairchild).

1964:

primo progetto di RAM statica MOS a circuito integrato (J. Schmidt, Fairchild).

1965:

introduzione dei circuiti integrati monolitici nei grandi calcolatori

elettronici (Burroughs B2500, RCA Spectra-70, SDS Sigma 7).

1965:

introduzione dei contenitori standardizzati in formato DIP (D. Forbes, R. Rice e

B. Rogers, Fairchild).

1965:

prime memorie ROM a circuito integrato TTL (Sylvania per Honeywell).

1965:

prime RAM statiche sperimentali a circuito integrato (B. Augusta, P. Castrucci).

1965:

primo circuito integrato con più di 500 transistor, uno shift-register da 100

bit di capacità (General Microelectronics).

1966:

prime RAM a circuito integrato

bipolare (T. Longo, Transitron per Honeywell).

1966:

introduzione dei primi programmi CAD per la progettazione dei circuiti integrati.

1966:

introduzione della tecnica "Self-Aligned Gate" per la fabbricazione di

integrati MOSFET (Bower e Dill).

1966:

sviluppo della

tecnologia "silicon gate" per la fabbricazione degli integrati

MOS (R. Kerwin, D. Klein e J. Sarace, Bell Labs).

1966:

prima memoria RAM a circuito integrato bipolare da 16 bit (IBM).

1966:

commercializzazione dei primi integrati logici ECL (Motorola).

1966:

invenzione della DRAM con cella a

singolo transistor (R. Dennard, IBM), il cui funzionamento si basa sulla

carica elettrica immagazzinata in una giunzione, "caricata" e

"scaricata" sotto il controllo di un transistor FET. Tutte le moderne

DRAM derivano da questo prototipo.

1967:

introduzione dei primi circuiti

integrati ASIC.

1967:

introduzione dei transistor NMOS nella realizzazione di memorie a semiconduttore

(Wegener, Lincoln, Pao, O'Connel, Oleksiak).

1968:

primo integrato MOS "silicon gate" commerciale (F. Faggin e D. Klein,

Fairchild - F3708).

1968:

sviluppo di DRAM MOS da 256 bit (L.Boysel, Fairchild).

1968:

introduzione di SRAM bipolari da 64 bit ad alta velocità (IBM).

1969:

invenzione della logica TTL-Schottky, che aumenta la velocità dei circuiti

integrati TTL.

1969:

prime DRAM MOS commerciali a circuito integrato da 1 e 2 Kbit (Four Phase

Systems e Advanced Memory Systems).

1969:

invenzione della tecnologia BiCMOS (Lin, Ho, Iyer e Kwong, "Complementary

MOS-Bipolar Transistor Structure").

1970:

le RAM MOS a circuito integrato superano in prestazioni ed affidabilità le

memorie a nuclei magnetici.

1970:

prima RAM (bipolare) da 256 bit per chip.

1971:

invenzione del microprocessore

(T. Hoff, S. Mazor, M. Shima e F. Faggin, Intel).

1971:

invenzione della EPROM

cancellabile mediante esposizione a radiazione UV (D. Frohman).

I primi

circuiti integrati ASIC

Negli anni Sessanta la richiesta da

parte dei fabbricanti di mainframe (grandi calcolatori) di dispositivi logici

veloci e con funzioni particolari portò alla nascita dei primi integrati ASIC

(specifici per una determinata applicazione), fabbricati su richiesta e secondo

le specifiche del cliente da case quali Fairchild e Signetics. I primi

calcolatori ad impiegare circuiti integrati furono lo Spectra 70 di RCA (1965)

ed i Burroughs 2500/3500 (1966). La macchina RCA utilizzava circuiti integrati

con logica CML (Current-Mode Logic) progettati internamente e realizzati da

Fairchild. Gli ingegneri della Burroughs cooperarono sempre con la Fairchild per

la realizzazione degli integrati CTL (Complementary Transistor Logic) impiegati

appunto nei sistemi 2500/3500 ed in altri calcolatori (ad esempio gli HP 3000).

Nel 1962 infine Motorola sviluppò la prima famiglia logica ECL, la MECL

impiegata in svariati progetti di mainframe e minicomputer durante gli anni

Sessanta e Settanta a motivo della sua velocità.

La maggior parte degli ASIC

appartengono a due categorie: "gate array" e "standard cell".

I gate array sono matrici di porte logiche (in origine di singoli transistor)

che possono essere connesse tra loro per formare un circuito complesso

corrispondente alle specifiche richieste dal cliente in fase di progetto. I

primi gate array commerciali sono stati nel 1967 i DTL/TTL 4500 della serie

MicroMatrix di Fairchild, contenenti 32 porte NAND. Questa famiglia consentiva la realizzazione di

circuiti logici personalizzati utilizzando appositi programmi di CAD.

All’inizio degli anni Settanta si affermò la famiglia ULA (Uncommitted Logic

Array) di Ferranti. Nel 1974 International Microcircuits introdusse invece la

prima famiglia di gate array CMOS. Gli ASIC "standard cell" sono

basati sull’assemblaggio in un unico circuito integrato di più blocchi

predefiniti che compongono una libreria (library) di funzioni logiche, note col

nome di "celle" (cells). I primi ASIC standard cell (MOS) furono

all’inizio degli anni Settanta le famiglie MicroMosaic di Fairchild e Polycell

di Motorola. L’impiego di programmi CAD per lo sviluppo degli ASIC venne reso

popolare da due produttori divenuti in seguito i principali protagonisti di

questo mercato: VLSI Technologies (fondata nel 1979) e LSI Logic (nata nel

1981).

La prima

ROM su circuito integrato

La ROM a circuito integrato (TTL)

venne introdotta nel 1965 da Sylvania con una capacità di 256 bit. Sempre nel

1965 venne introdotta da parte di General Microelectronics la prima ROM MOS,

più lenta ma di maggiore capacità (1.024 bit).

Vedi: http://www.computerhistory.org/semiconductor/timeline/1965-ROM.html.

Le prime

SRAM su circuito integrato

La prima RAM statica (SRAM) realizzata

come circuito integrato (bipolare) venne brevettata nel 1963 da R. Norman della

Fairchild. Nel 1965 dalla collaborazione tra IBM, Signetics e Scientific Data

Systems (SDS) nacque la SRAM TTL SP95, con una capacità di 16 bit, impiegata

nel calcolatore System/360 Model 95, originariamente progettato per la NASA. Nel 1966 venne presentata

la RAM statica da 16

bit, anch'essa TTL, TMC3162 fabbricata da Transitron ed utilizzata da Honeywell

in diversi minicomputer tra i quali il 4200. Altre SRAM di prima generazione da

16 bit sono la Fairchild 9033, la Sylvania SM-80 e la SN7481 di Texas

Instruments. Tra le più vecchie memorie statiche a 64 bit ci sono invece la

Texas Instruments SN7489, l'Intel 3101 (1969) e le Fairchild 9035 e 93403

(1969/70). All'inizio degli anni Settanta vennero fabbricate le prime SRAM da

128 e da 256 bit, usate inizialmente in calcolatori quali l'IBM System/360 Model

145 e l'ILLIAC IV (1970). La prima RAM statica TTL a 256 bit è stata la

Fairchild 93410 (1970). Nel 1976 fecero la loro comparsa le SRAM bipolari da 1

kbit (1.024 bit), TTL ed ECL, tra cui la Fairchild 10415 impiegata nel

supercomputer Cray 1.

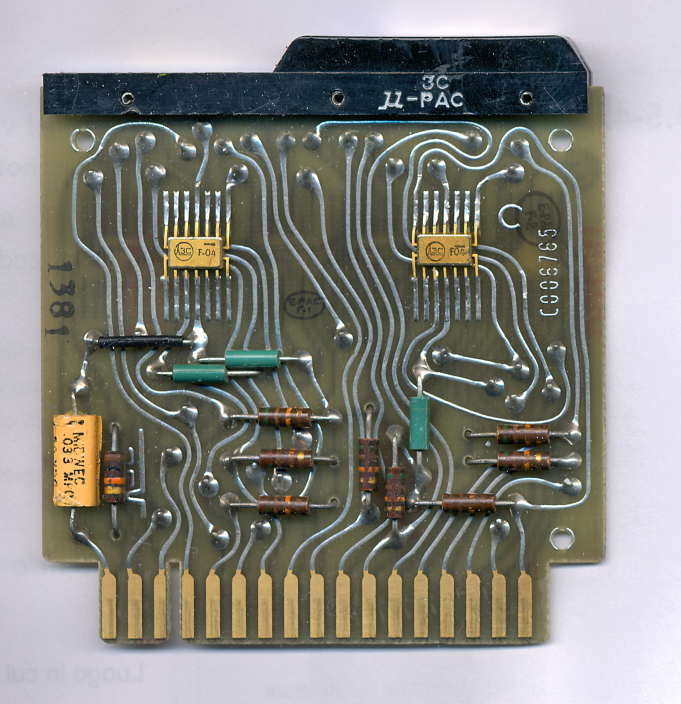

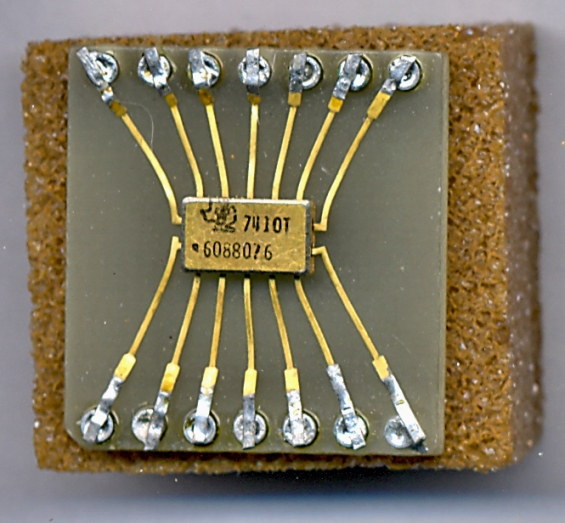

Schedina con integrati 3C Micro-PAC

(fine anni Sessanta). "3C" è l'acronimo di Computer Control Company,

società fondata nel 1953 da ex-impiegati della Raytheon (vedi: http://www.series16.adrianwise.co.uk/history/ccc.html).

La 3C produceva principalmente apparecchiature elettroniche per il Ministero

della Difesa USA. Sviluppò a partire dalla fine degli anni Cinquanta una serie

di moduli logici standardizzati da impiegare nella progettazione di calcolatori

elettronici ed altri apparati. La prima serie, basata su valvole, uscì col nome

di "V-PAC"; venne quindi rimpiazzata nel 1959 dall'equivalente a

transistor (T-PAC). Nel 1960 3C introdusse la serie "S-PAC" a basso

consumo. Quest'ultima fu utilizzata nella realizzazione del DDP-116

(1963), un calcolatore noto per essere stato il primo minicomputer commerciale a

16 bit. Nel 1966 venne infine introdotto il suo successore DDP-516

la cui logica si basava sui moduli Micro-PAC o M-PAC del tipo di quello

raffigurato qui sopra. Questi moduli sono stati una delle primissime

applicazioni commerciali dei circuiti integrati logici. I moduli S-PAC e

Micro-PAC vennero impiegati anche come base per le apparecchiature digitali

sviluppate da 3C per il settore aerospaziale, ad esempio per le sonde

Mariner della NASA. Sempre nel 1966 3C venne venduta alla Honeywell di cui

diventò una divisione nota col nome di "Computer Control Division", e

tale rimase fino al 1970. Vedi anche: http://www.series16.adrianwise.co.uk/history/TCMR-V15.html.

Vedi: http://www.vintchip.com/COMPUTER/COMPBOARD.html.

In particolare: http://www.vintchip.com/COMPUTER/3CBOARD-1.JPG

(moduli simili a quello qui raffigurato).

Vedi: http://www.series16.adrianwise.co.uk/collection/restoration.html.

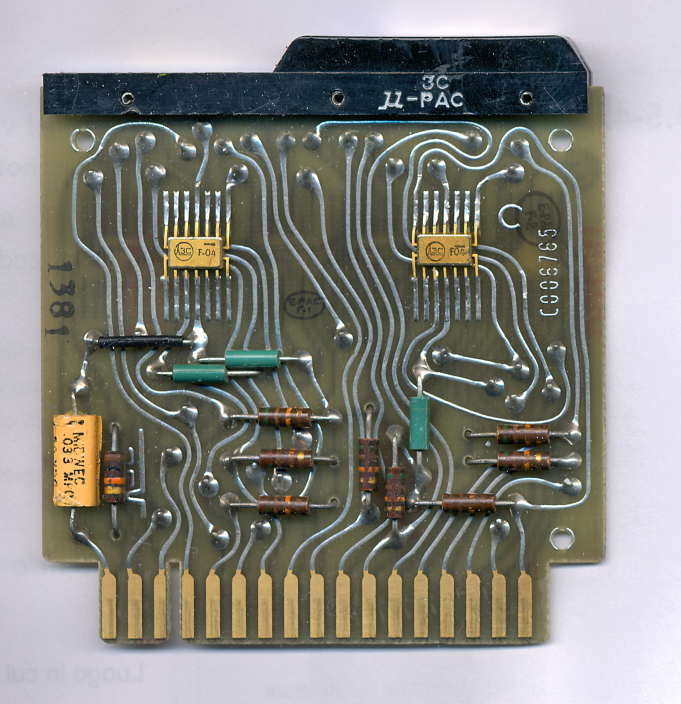

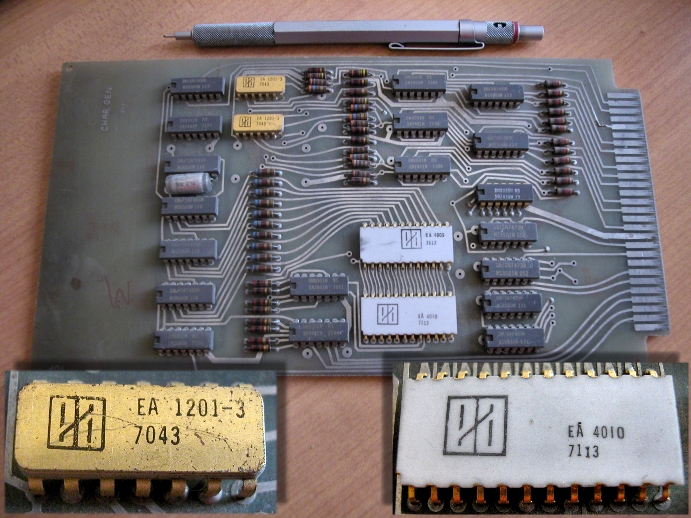

Scheda generatrice di caratteri (character

generator) per terminale video, 1971, con integrati fabbricati da Electronic

Arrays: in basso a sinistra uno shift register EA1201 e a destra una ROM MOS

EA4010.

Vedi: http://www.cpushack.com/2009/02/11/eprom-of-the-week-electronic-arrays-ea2708/,

oppure questa

pagina.

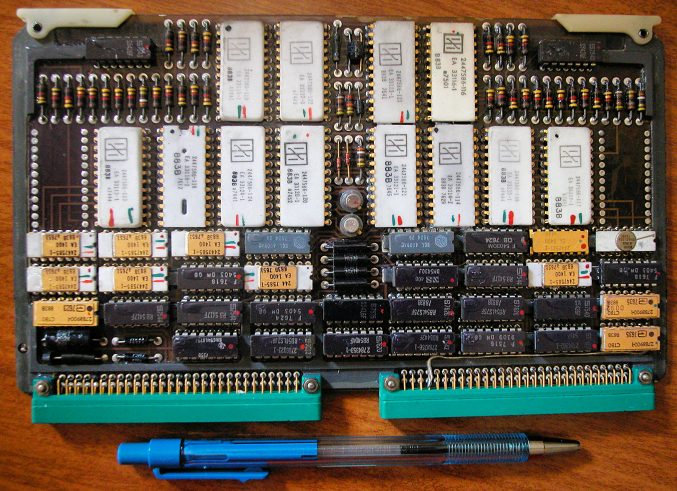

Un'altra scheda con

integrati Electronic

Arrays (memorie masked-ROM bipolari), in questo caso uno dei moduli di un

calcolatore militare del 1976 (non conosco il modello né il fabbricante). Sulla

scheda si trovano integrati di parecchie case diverse, a parte la EA (Electronic

Arrays): RCA, Signetics, Fairchild, Texas Instruments, Solid-State Scientific

(poi Thomson-CSF), National Semiconductor. Vedi: http://www.computerhistory.org/semiconductor/companies.html.

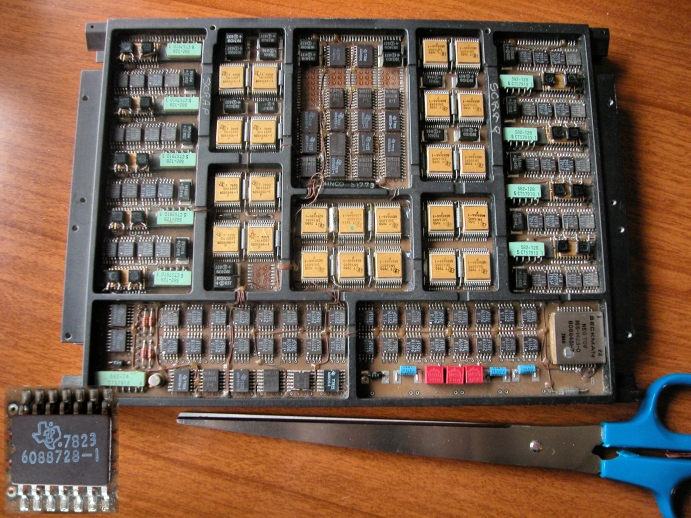

Questa scheda IBM del

1976 (a quale macchina apparteneva? qualche idea in proposito? mi è stato

indicato che potrebbe aver fatto parte di un IBM 3790 Communications System, http://ed-thelen.org/comp-hist/IBM-ProdAnn/3790.pdf) contiene integrati

FET LSI (i componenti ceramici bianchi, in basso un dettaglio dei piedini,

dei quali uno isolato), moduli MST e integrati TTL standard fabbricati da Texas

Instruments, National e Signetics. Questo tipo di integrati (FET LSI) è stato

utilizzato anche nell'IBM 3740 Data Entry System del 1973 (vedi: http://www-03.ibm.com/ibm/history/exhibits/rochester/rochester_4016.html),

che è stato il primo prodotto commerciale IBM ad utilizzare tale tecnologia.

Detto per inciso l'IBM 3790, annunciato nel 1975, è stato uno dei primissimi

sistemi distribuiti (vedi: http://en.wikipedia.org/wiki/IBM_3790)

nonché l'antenato diretto del più noto IBM 8100, diffuso anche nel nostro

Paese in molte aziende ed Amministrazioni pubbliche (vedi ad esempio, per quanto

riguarda l'INPS, questo

documento del 1981).

Per il 3740, vedi anche

qui: http://ed-thelen.org/comp-hist/IBM-ProdAnn/3740.pdf.

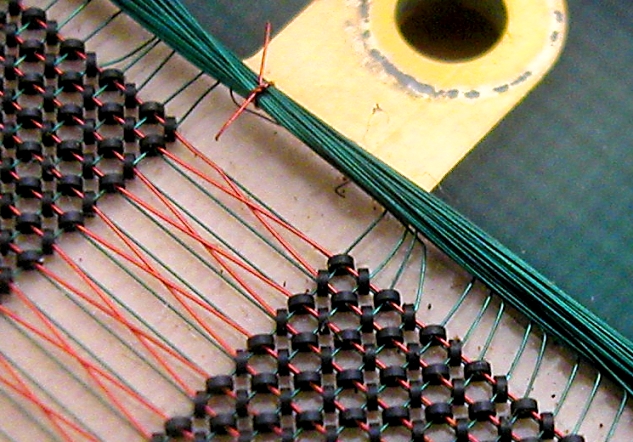

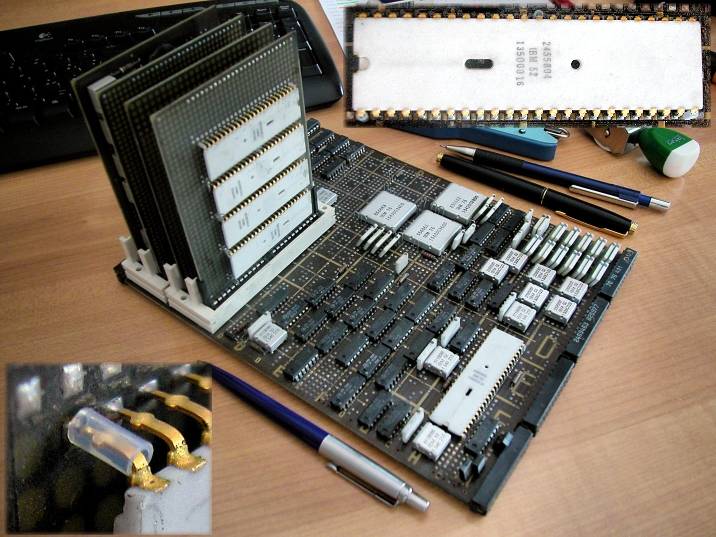

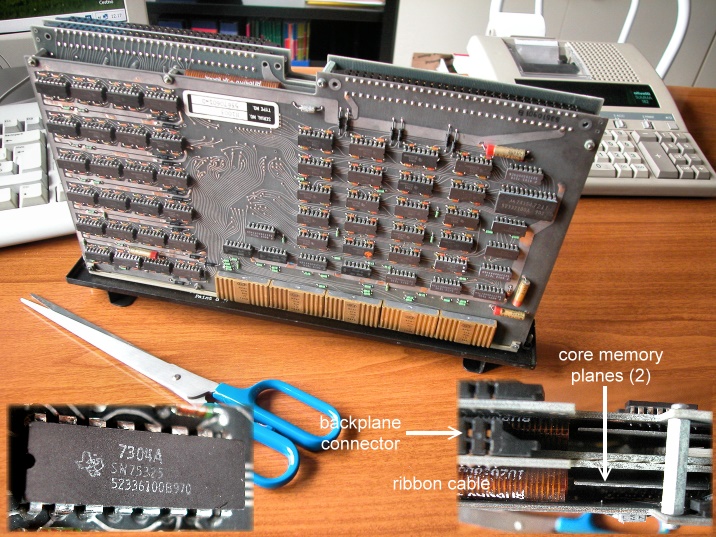

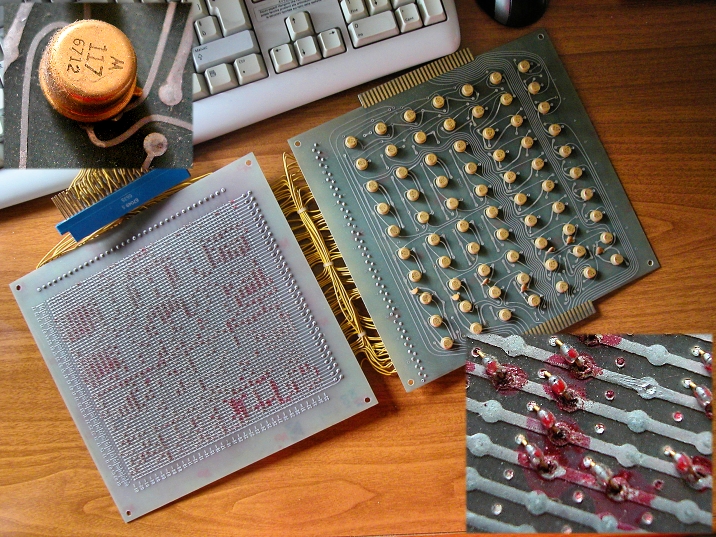

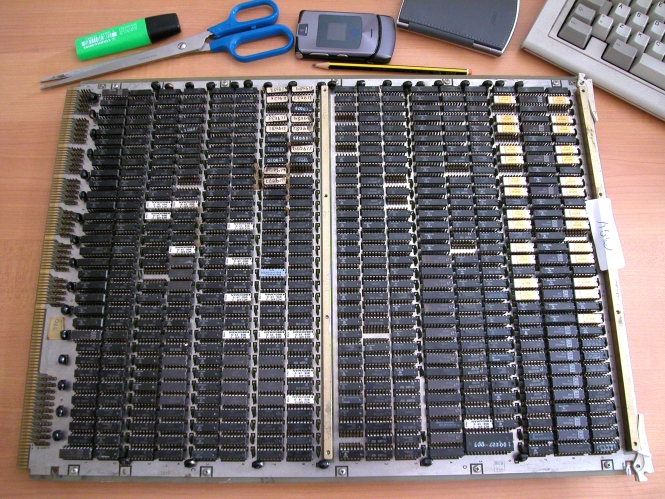

Memoria a nuclei magnetici fabbricata

da CDC, 1973 (capacità 32 Kword). Apparteneva probabilmente ad un CDC 3500,

un calcolatore con CPU a 48 bit appartenente alla famiglia CDC 3000 (1965/7).

Sulle tre schede riunite in un unico modulo (vedi dettaglio in basso a destra)

si trovano integrati TTL Texas Instruments delle Serie 74 e 75. Nel dettaglio in

basso a sinistra è visibile un Memory Core Driver SN75325 (vedi: http://ed-thelen.org/comp-hist/Byte/76jul.html,

http://penguincentral.com/docs/04.htm).

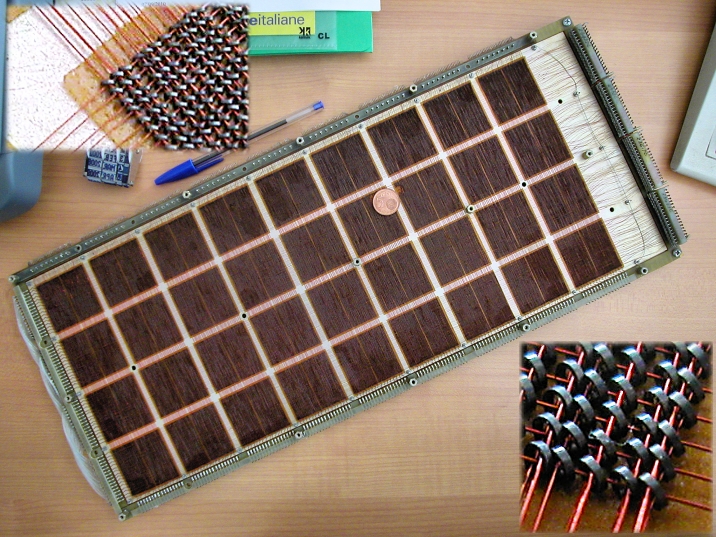

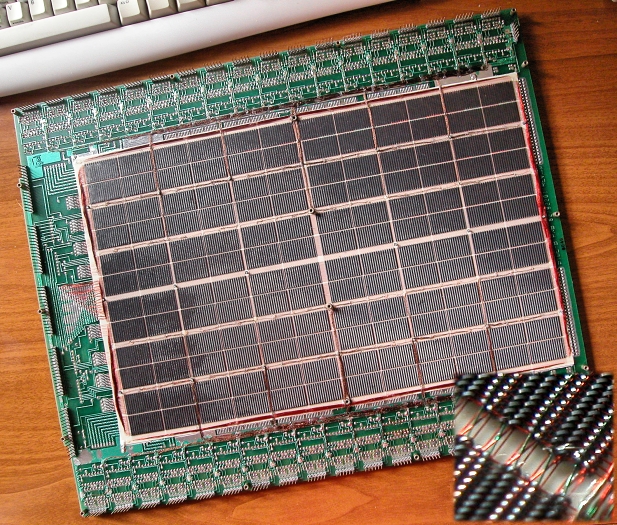

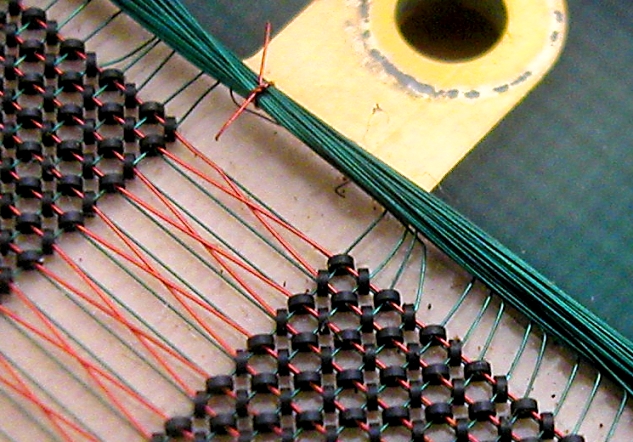

Questa RAM a nuclei magnetici

fabbricata da Electronic Memories nel 1968 ha una capacità di 72 kbit. In alto

a sinistra un dettaglio e, in basso a destra, una vista ravvicinata dei nuclei.

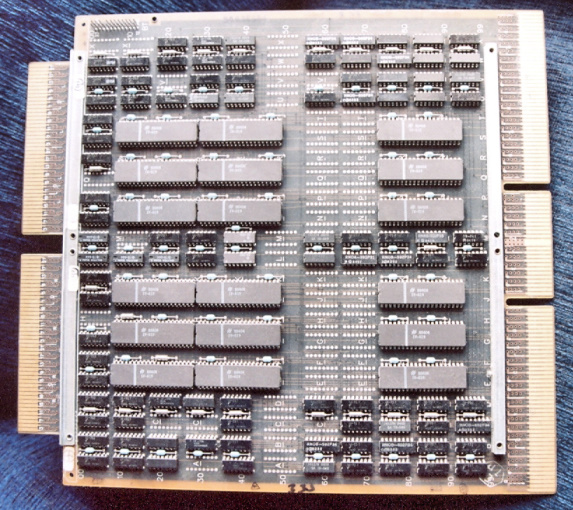

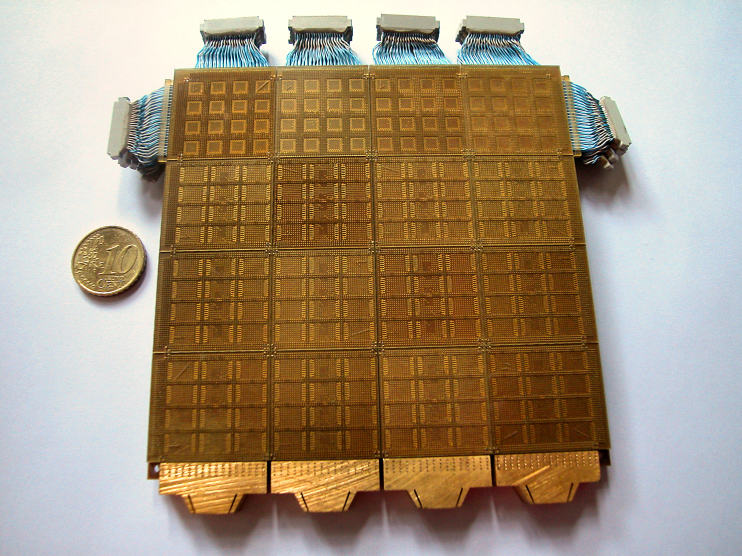

Scheda di memoria RAM a nuclei

magnetici appartenuta ad un calcolatore CDC Cyber (1969). La capacità è

di 64 K per 16 bit. Questa è una delle schede di memoria a nuclei di più alta

capacità singola. In basso a destra un dettaglio dei nuclei.

Memoria a nuclei magnetici (1978),

impiegata forse in un calcolatore IBM System/4. Tutti i circuiti integrati (TTL?)

sono contenuti in package ceramici SMT e sono fabbricati da Texas Instruments

(in basso a sinistra un dettaglio) oppure da AMD.

Sulle memorie a nuclei

vedi: http://www.thecorememory.com/BYTE_July_1976_-_Coincident_Current_Ferrite_Core_Memories.pdf.

Sulle

"antiche" tecnologie delle memorie: http://www.thecorememory.com/ComputerMemories.pdf.

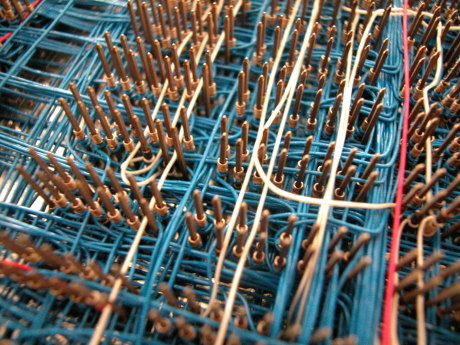

Dettaglio della memoria

a nuclei magnetici NCR da 8 kbit visibile più in basso (faceva parte

dell'elettronica di un terminale POS del 1977). I fili di colore arancione sono

i "sense/inhibit wire" che servono per la lettura della memoria.

Ciascun nucleo è attraversato da 3 fili: due di controllo, verdi ("drive

lines") ed uno di lettura. Tutte le memorie a nuclei, con l'eccezione delle

prime realizzate che si basavano invece su quattro fili (le funzioni "sense"

ed "inhibit" erano svolte da due fili separati), seguono questo

schema. Il lato lungo

dell'immagine è pari, nella realtà, a circa 1 cm (Nikon Coolpix 5000).

Vedi: http://ed-thelen.org/comp-hist/navy-core-memory-desc.html;

http://www.science.uva.nl/museum/CoreMemory.html.

Campioni (sample) di elementi

magnetici BIAX, fabbricati dalla Aeronutronic Division della Ford (circa

1965). Si tratta di blocchetti di ferrite dotati di due fori con assi fra loro

perpendicolari (BIAX è acronimo

di BI-AXial), ognuno di quali è attraversato da un filo conduttore che serve

per la scrittura e, rispettivamente, per la lettura.

Questi elementi possono essere utilizzati per la realizzazione sia di porte

logiche (gate, negli anni Sessanta non era così insolito l'uso di elementi

magnetici per ottenere circuiti logici digitali) che di memorie. Queste ultime,

rispetto alle ordinarie RAM a nuclei, avevano due vantaggi: il primo consisteva

nel fatto che la lettura era non distruttiva (NDRO, Non-Destructive ReadOut),

cioè non implicava la cancellazione e la seguente ri-scrittura del contenuto di

una data locazione di memoria; il secondo, che ciascun elemento veniva

controllato con due soli fili, anziché con tre. Questo genere di memorie però,

al pari di altre RAM NDRO dell'epoca (ad es. il Fluxlok, transfluxor e la plated-wire

memory) non ha avuto successo commerciale, in primo luogo a causa dei costi

elevati e dell'altrettanto elevato ingombro (se paragonato ai classici nuclei).

Memorie basate su elementi BIAX sono state tuttavia impiegate in svariate

applicazioni (calcolatori di bordo, ad esempio) dalla NASA, come si può leggere

qui

(si ricordi che le memorie a nuclei magnetici sono poco sensibili all'effetto

delle radiazioni, dunque si adattano bene agli impieghi aerospaziali). Tra i

pochi computer che hanno usato memorie BIAX c'è il Packard Bell 440 del 1964,

vedi ad es. in http://ed-thelen.org/comp-hist/BRL64-p.html

e l'Univac LARC.

"The BIAX digital computer elements

are completely new magnetic memory and logic elements. They are

multi-aperture devices fabricated out of conventional ferrite materials and

are, generally speaking, an order of magnitude faster than present magnetic

devices. To attain these speeds, they employ a fundamentally different

principle of operation than is used with existing ferrite core and

multi-aperture units. The BIAX principle employed is one of flux

interference, not flux steering as is common in most multi-aperture devices.

In addition to increased speeds, the BIAX elements also have important

environmental advantages and are capable of operation at high temperatures.

Another important advantage of the elements is their non-destructive read

characteristic. Important cost savings also appear to be achievable with

these units, particularly in terms of the logic elements. These BIAX memory

and logic elements are the result of approximately two and one half years of

work conducted in Aeronutronic's Computer Research Laboratory. The elements

have been reduced to practice and are currently in production. Aeronutronic

is applying these BIAX techniques to a number of commercial and military

projects where multi-megacycle data processing is a requirement."

Vedi: http://www.computerhistory.org/collections/accession/102646214.

Vedi: http://www.thecorememory.com/NCR_Hanlon.pdf

(IEEE Transactions on Electronic Computers, vol. EC-15 no. 4, Aug 1966).

Anche: http://www.thecorememory.com/NCR_Kaufman.pdf

(stessa fonte).

Specifiche di questo

elemento BIAX: http://archive.computerhistory.org/resources/text/Ford/FordMotor.BIAX-M-145-05.1963.102646214.pdf.

Anche: http://www.quadibloc.com/comp/cp01.htm.

Anche: http://portal.acm.org/citation.cfm?id=612257&dl=GUIDE&coll=GUIDE&CFID=89058227&CFTOKEN=25341516.

Anche questa

pagina di IEEExplore (richiede la registrazione).

Anche: http://oai.dtic.mil/oai/oai?verb=getRecord&metadataPrefix=html&identifier=AD0655355.

Memoria ROM a

"matrice di diodi" ("diode-matrix ROM"), 1967, il

fabbricante è sconosciuto. Tecnicamente è equivalente ad una ROM a maschera (mask

ROM). Questo tipo di ROM era usato negli anni Sessanta e Settanta come firmware,

più precisamente come memorie per il microcodice

(control store), o come memoria di

boot in molti calcolatori elettronici, piccoli e grandi.

Le varie istruzioni sono permanentemente "memorizzate" collegando dei

diodi (visibili nel dettaglio in basso a destra) in corrispondenza dei

desiderati incroci tra le righe (word-line) e le colonne (bit-line) di una

matrice di dimensione prefissata. Altri impieghi comuni delle ROM a matrice di

diodi erano la codifica della tastiera e dei caratteri a video nei terminali e

la programmazione delle calcolatrici elettroniche da tavolo. La scheda a destra

contiene integrati RTL Motorola in package TO-99.

Classico esempio di

boot-ROM a matrice di diodi: una scheda DEC M847 (1975), per PDP-8. Questa

memoria contiene solo le poche istruzioni necessarie all'avvio del sistema ed al

caricamento del sistema operativo (bootstrap). La capacità è di 32 word (parole di

memoria) a 12 bit (il PDP-8 è un minicomputer a 12 bit, appunto). Vi sono in

tutto 64 colonne di diodi, ciascuna delle quali corrisponde ad una half-word

(mezza parola di memoria) da 6 bit. La presenza di un diodo corrisponde alla

memorizzazione in quella posizione di un "1" binario.

Scheda di calcolatore (1974, il

fabbricante non è identificabile con certezza) interamente realizzata con

circuiti logici (TTL) a

bassa scala di integrazione prodotti da Fairchild (dettaglio), appartenenti alla

serie 9000 "Micrologic" (alternativa alla più nota "Serie

74"). La maggior parte dei

minicomputer degli anni Settanta è basata su circuiti realizzati con integrati

(bipolari) logici TTL di questo tipo ed in particolare, appunto, della "Serie 74"

che è divenuta rapidamente uno standard industriale universalmente riconosciuto. Nel periodo compreso tra la metà degli anni Sessanta e quella dei

Settanta sono state sviluppate molte diverse famiglie di circuiti logici SSI,

tanto TTL che DTL (Diode-Transistor Logic), RTL (Resistor-Transistor Logic) ed

ECL (Emitter-Coupled Logic). La gran parte di esse è scomparsa dal mercato nel

giro di pochi anni ed alcune non hanno mai raggiunto la produzione di massa.

Praticamente tutti i fabbricanti di circuiti integrati (vedi Fairchild, Motorola,

Signetics, Philips...) avevano all’epoca in catalogo una o più famiglie

logiche di vario tipo. Fairchild è stata nel 1964 il primo produttore di

integrati logici commerciali (di tipo RTL).

Vedi: http://wps.com/archives/solid-state-datasheets/index.html#BYNUM.

Scheda "disk controller" per

minicomputer Data General NOVA, 1978, realizzata con integrati TTL a bassa scala

di integrazione ed alcune memorie ROM (a destra, fabbricate da Intersil). In

basso a sinistra un dettaglio dei circuiti contraddistinti dal marchio di Data

General.

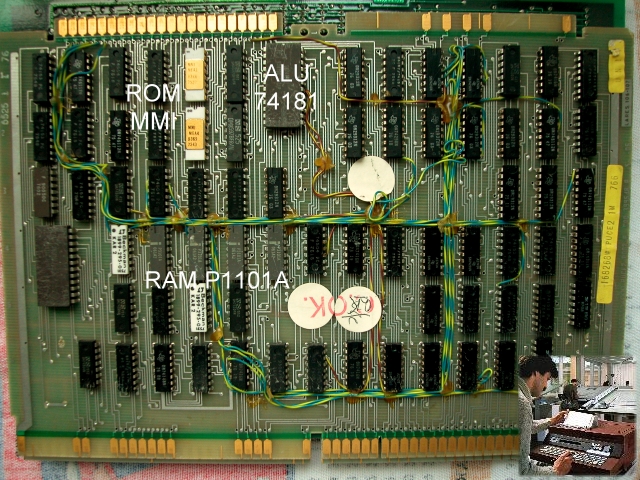

Schede di calcolatori elettronici

digitali (una fabbricata da Transidyne General Inc., 1973, l’altra da Triumph

Adler, 1972) che utilizzano circuiti integrati logici TTL e componenti a media

scala di integrazione quali memorie ROM da 512 byte, ALU 74181 e shift-register

a 32 bit Texas Instruments TMS3112.

Prima

famiglia commerciale di integrati logici CMOS - First

commercial family of logic CMOS ICs (RCA CD4000)

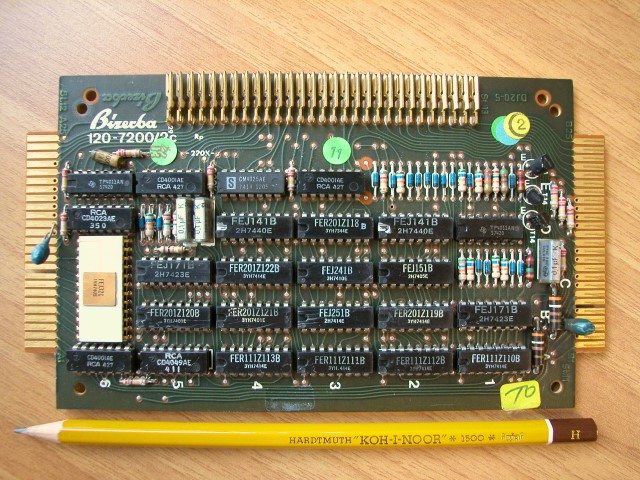

Unità aritmetica (ALU) di un

registratore di cassa Bizerba (1974) fabbricata con integrati TTL e CMOS a

bassa/media scala di integrazione. Sulla scheda, visibili in basso a sinistra,

si trovano alcuni circuiti logici a bassa scala di integrazione (SSI) CMOS della

"Serie 4000", appartenenti all’originaria famiglia "CD4000

COS/MOS" prodotta da RCA a partire dal 1969, come alternativa a basso

consumo alla Serie 74. La "Serie 4000" è stata la prima famiglia di

integrati logici MOS di successo; durante gli anni Settanta ed Ottanta

praticamente tutti i principali fabbricanti di chip (in modo particolare

Motorola) hanno prodotto circuiti di questa serie. La famiglia di integrati

logici Philips FE deriva dalla precedente serie DTL FC (1967), di cui è

una trasposizione in TTL; in questi circuiti, la terza lettera della sigla

indica il tipo di dispositivo, inteso come "categoria" di circuito

logico: ad es. "H" denota le comuni funzioni logiche elementari (gate)

AND, NAND, OR ecc.; "J" i flip-flop, "K" i monostabili e

così via.

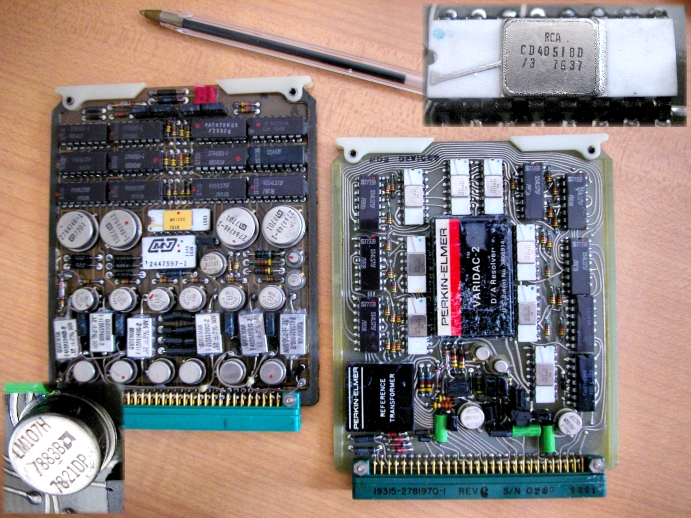

Due schede di un calcolatore militare

con integrati TTL della Serie 74 e circuiti MOS fabbricati da RCA (1977), in

alto un multiplexer/demultiplexer CD4051BD del 1976; in basso a sinistra un

amplificatore operazionale AMD LM107H, funzionalmente equivalente ai ben noti

LM101 e 741. Tutti i componenti sono rivestiti di resina epossidica trasparente

per proteggerli dall'umidità. I componenti rotondi (package TO) più grandi

sono amplificatori operazionali fabbricati da General Instrument.

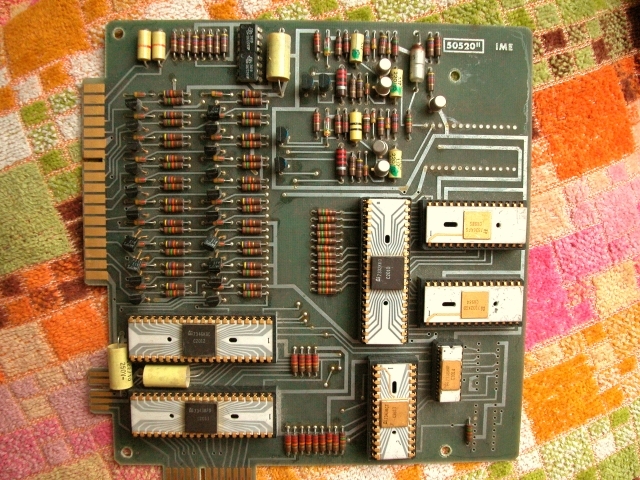

Elettronica di una calcolatrice da

tavolo IME (Industria Macchine Elettroniche, società del Gruppo Edison, 1973)

basata su circuiti integrati AMI (American Micro-systems Inc.). AMI, fondata nel

1966, è stata uno dei primi fabbricanti di integrati MSI/LSI MOS. Ha realizzato

circuiti custom per quasi tutti i principali produttori dell’epoca (vedi).

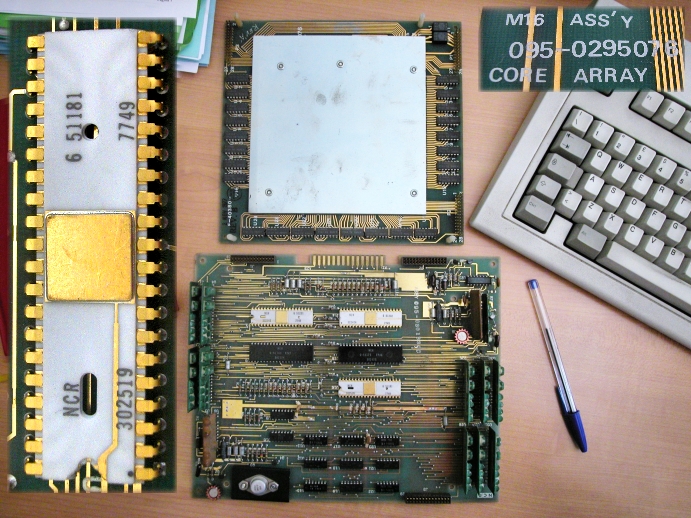

La logica di un terminale POS

fabbricato dalla NCR (1977), con integrati LSI MOS (a sinistra un dettaglio),

circuiti ibridi e una memoria a nuclei magnetici da 8 kbit (in alto a destra un

dettaglio).

Un assemblaggio simile

(sempre NCR): http://retro.co.za/ccc/.

Prima

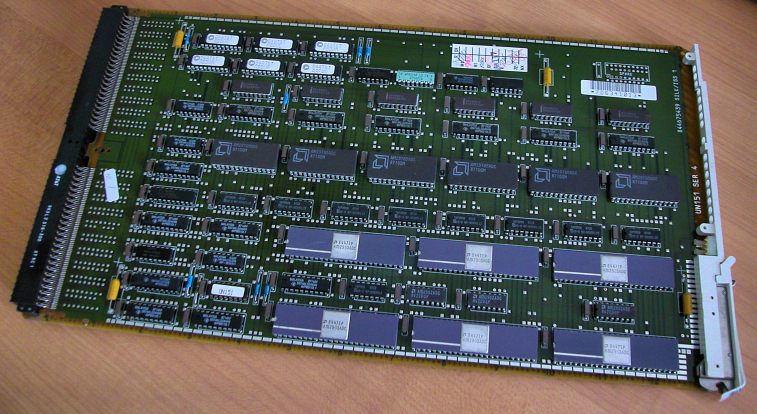

ALU completa in singolo chip - First single-chip