Cray on a chip: il microprocessore Intel i860

Il processore Intel i860 (oppure 80860, nome in codice N10, da non confondersi con il quasi omonimo chipset Intel per sistemi Pentium III Xeon, l’860), molto modestamente soprannominato dal produttore Cray on a chip (vedi più sotto), è una CPU RISC ad alte prestazioni introdotta nel 1989 ed uno dei tentativi (falliti: vedi il famigerato progetto iAPX432) della Casa di Santa Clara di dar vita ad un’architettura di successo completamente diversa rispetto al suo prodotto più diffuso, la x86, non esattamente un capolavoro dal punto di vista tecnologico. Presentato con toni trionfalistici, ha conosciuto nella “vita reale” uno scarso successo a causa delle prestazioni effettive inferiori a quelle dichiarate (teoriche) e dell’elevato costo, trovando posto solo in alcune applicazioni particolari nel settore della grafica tridimensionale e del calcolo parallelo. Benché la sua rumorosa discesa in campo abbia oscurato quella, ben più tranquilla, dell’altro RISC tradizionale di Intel, l’i960, quest’ultimo ha ottenuto al contrario un larghissimo consenso, rimanendo a tutt’oggi nelle sue numerose varianti uno dei processori RISC più diffusi in assoluto.

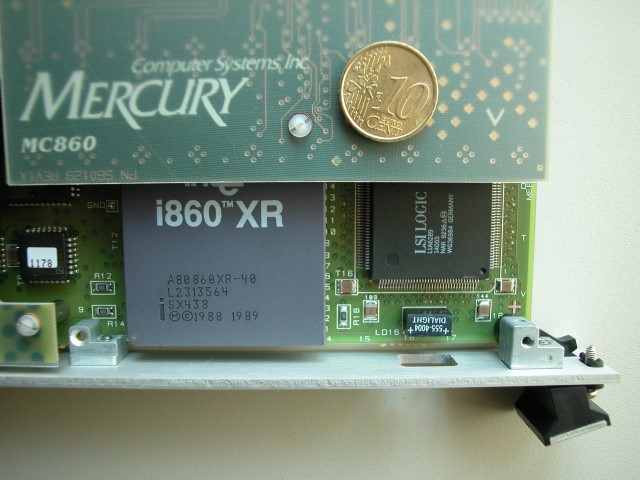

Processore Intel i860, versione XR a 40 MHz, utilizzato in una scheda VME MC860 prodotta da Mercury. Questa scheda, introdotta nel 1990, è stata una delle prime soluzioni per numerical intensive computing disponibili a prezzi ragionevoli (vedi la sezione storica nel sito di Mercury Inc.)

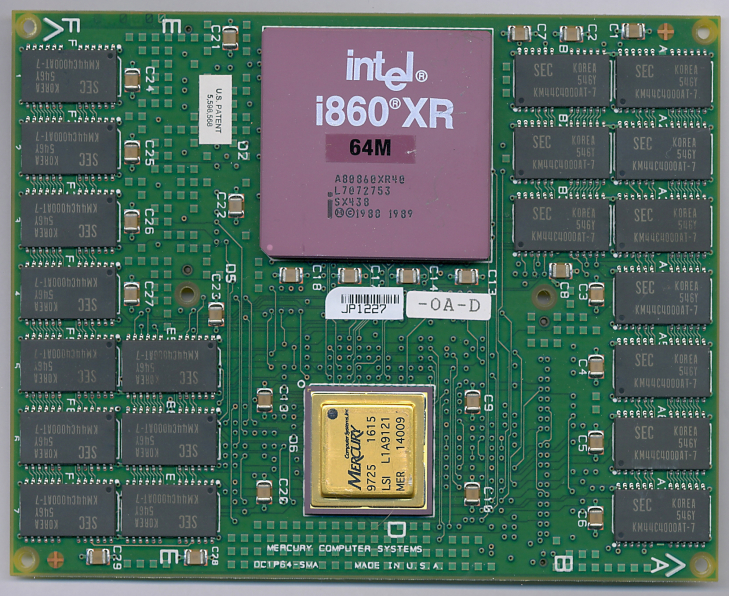

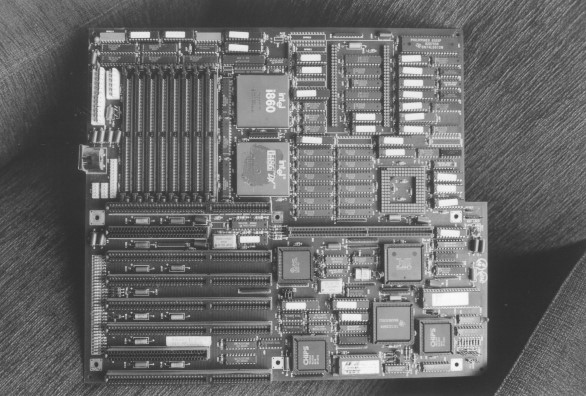

Scheda VME Mercury Race MCV6 (1997) con quattro CPU Intel i860XR-40, ciascuna affiancata da 16 MB di RAM locale. Questa piattaforma RISC è stata utilizzata in numerose applicazioni scientifiche ed ingegneristiche laddove erano richieste notevole capacità di calcolo e buona scalabilità (più schede identiche potevano essere impiegate a formare un sistema multiprocessore con 8, 16... CPU). La scheda è suddivisa in quattro "nodi" (CN, Computing Node) ciascuno dei quali contiene un processore i860, la memoria locale ed un ASIC di interfaccia. La potenza di calcolo dichiarata è di circa 320 MFLOPS. Vedi: http://www.artisan-scientific.com/info/Mercury_MCV6_Datasheet.pdf.

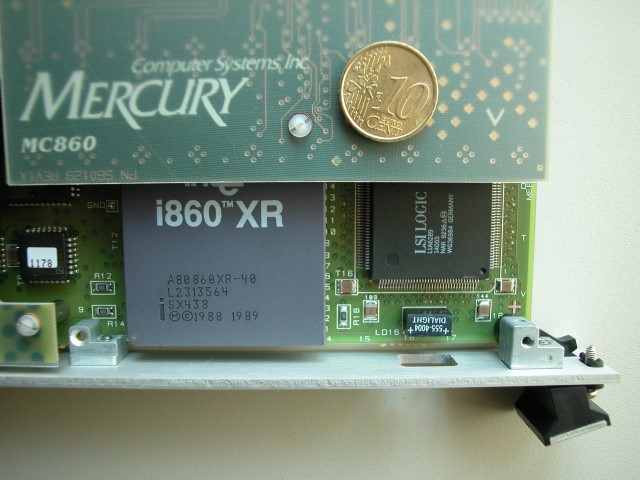

Modulo a singola CPU per scheda Mercury Race MCV-6, con processore Intel i860XR-40 e 64 MB di RAM locale (suddivisa in 4 banchi da 16 MB).

CPU Intel i860XR-40 impiegata come geometry-engine in una scheda grafica GA-5000 (bus VME) del 1994.

CPU i860XR a 40 MHz impiegata in una scheda IBM HPS per RS/6000 SP.

Microprocessori

e supercomputer

Alla metà degli anni Ottanta la tecnologia dei microprocessori si era evoluta a tal punto da consentire la realizzazione dei cosiddetti “supermicro”, processori cioè in grado di eguagliare e perfino superare le prestazioni di parecchi grandi elaboratori allora in uso i quali, contrariamente a quanto accade oggi, erano realizzati senza ricorrere ai microprocessori stessi – il cui campo d’azione appariva ancora limitato al personal computing, alle workstation ed ai server di rete, alle applicazioni embedded. Dal punto di vista della potenza di calcolo, le macchine costruite dalla Cray Inc. (allora Cray Research Inc., fondata nel 1972 dal mostro sacro dell’informatica Seymour Cray, che fino ad allora aveva lavorato per la ERA prima e per la CDC poi, dando un fondamentale impulso alla realizzazione dei primi supercomputer), costituivano il termine di paragone ed il modello cui ispirarsi; il Cray – 1, capace nel 1972 di 80 MFLOPS, aveva dato vita ad un’invidiata famiglia di super – calcolatori che estesero i limiti dell’informatica ben al di là di ciò che molti, in specie i non addetti ai lavori, avrebbero mai immaginato. Anche se a costoro pareva ancora impossibile, gli esperti del settore sapevano già da tempo che prima o poi sarebbe arrivato il momento in cui un microprocessore avrebbe potuto sviluppare una potenza di calcolo uguale, o anche superiore, a quella d’una simile macchina. Se oggi un comune Pentium 4 è parecchio più veloce di essa, nel 1989 i microprocessori avevano ancora parecchia strada da compiere prima di potersi misurare ad armi pari con i grandi calcolatori. Fece quindi sensazione alla fine del 1988 il comunicato di Intel nel quale si annunciava l’imminente rilascio di un microprocessore accreditato di 60 e più MFLOPS, degno dunque di essere soprannominato “Cray on a chip”, titolo del quale si fregiò in seguito pure il MIPS R8000 (curiosamente anch’esso utilizzato in macchine SGI, casa che ha stretti legami di parentela con la Cray). Il chip in questione era per l’appunto l’i860, con quel “60” che stava ad indicarne dunque la potenza di calcolo, una CPU senza dubbio molto avanzata per l’epoca e sotto certi aspetti perfino rivoluzionaria.

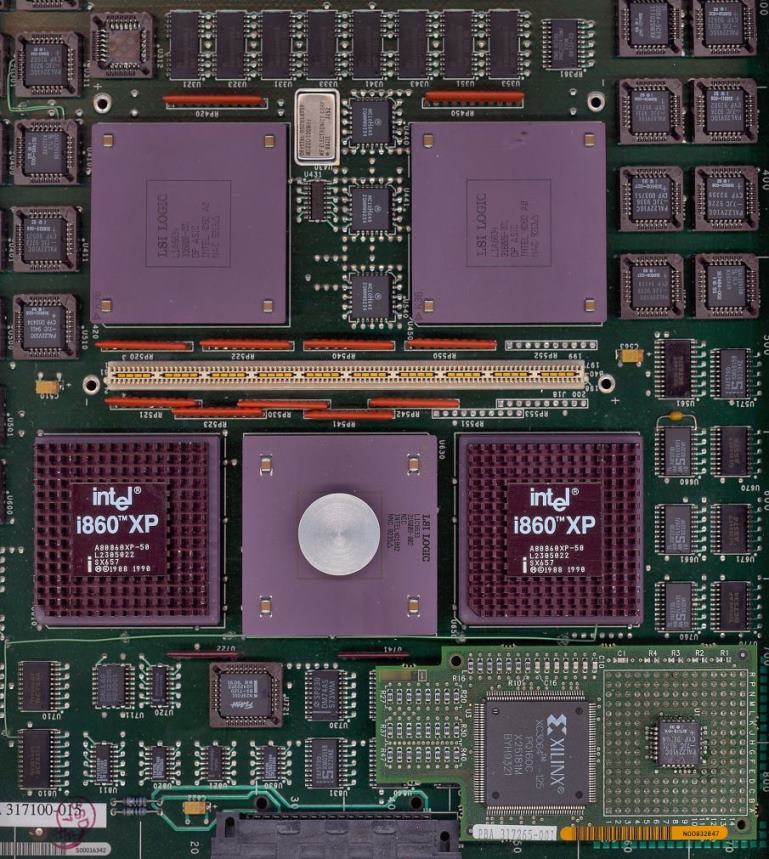

Tre processori Intel 80860XP-50 in una delle schede (node board - MP16) di un supercalcolatore di tipo MIMD a parallelismo massiccio Intel Paragon XP/S (presentato nel 1992, commercializzato a partire dal 1993). Il Paragon XP era una macchina parallela derivata dal progetto sperimentale "Touchstone DELTA" sviluppato dal Caltech all’inizio degli anni Novanta. Poteva contenere un massimo di 2K (2.048) CPU i860 a 50 MHz (successivamente 4.096, e 32 nella versione a basso costo XP/E) disposti a formare una matrice bidimensionale. La versione XP/S con 4.096 CPU raggiungeva una potenza di calcolo in virgola mobile di circa 300 GFLOPs (stimando in 60 MFLOPs la potenza di un singolo processore i860XP). Le CPU di un calcolatore Paragon XP/S sono suddivise su più schede chiamate "node boards", ciascuna delle quali contiene tre processori i860XP: due per il calcolo vero e proprio (application processors) ed uno per la gestione dei messaggi e dell’interazione col sistema operativo (message processor). La RAM di sistema è ripartita tra queste schede ciascuna delle quali contiene 16 o 32 MB. La comunicazione tra le node board è gestita da appositi chip VLSI chiamati "Paragon Mesh Routing Chips". L’ampiezza di banda della comunicazione da nodo a nodo è di circa 175 MB/s.

Vedi: http://ed-thelen.org/comp-hist/intel-paragon.html; anche: http://www.pact.sscc.ru/hardware/computer/.

Immagine di un calcolatore Intel Paragon XP/S installato nel 1992 presso l’ORNL (Oak Ridge National Laboratory) negli USA.

Node-board GP di un supercalcolatore a parallelismo massiccio Intel Paragon XP/S 5 (Touchstone Sigma), 1991/2. Una macchina completa aveva da 32 a 512 di queste schede: http://www.csm.ornl.gov/SC98/timetab.html.

21.4.2017 - Dettaglio di una scheda identica a quella riprodotta sopra. Sono visibili i due processori i860XP a 50 MHz con i rispettivi controller di memoria e l'interfaccia di rete da e verso gli altri nodi di calcolo (il chip LSI Logic con il dissipatore di calore rotondo). Il connettore bianco al centro dell'immagine serve ad alloggiare un'espansione della memoria RAM locale, una parte della quale è visibile nella parte alta della foto.

Scheda di I/O (MIO Board) di un supercalcolatore Intel Paragon XP/S. Ha una porta SCSI ed una AUI. Nei supercalcolatori Paragon le schede di I/O, basate su CPU i860 come le nodeboard, non eseguono programmi utente ma solamente specifici task assegnati dal sistema operativo.

12 processori i860XP-50 utilizzati in una scheda Silicon Graphics GE-10, parte del processore grafico ad alte prestazioni Reality Engine 2, utilizzata nelle macchine SGI Onyx (vedi questo sito per una descrizione più dettagliata, oppure le pagine della sezione hardware di majix's Obsolete Stuff).

Grandi

potenzialità

ma scarse

prestazioni

L’i860 era sì un processore RISC (al tempo – fu ideato nel 1986 – ne esistevano già alcuni), ma combinava caratteristiche diverse in un insieme a suo modo unico: utilizzava ad esempio un approccio di tipo VLIW, simile a quello dei DSP; la sua unità in virgola mobile (FPU) era interamente a 64 bit, suddivisa in tre parti (addizionatore, moltiplicatore, “processore grafico” per il trattamento di vettori di dati[1], un po’ una versione ante litteram dell’MMX, che difatti fu da esso influenzato). Di più, dal momento che esso possedeva tre separate pipeline, due per gl’interi ed una per la virgola mobile, poteva eseguire tre istruzioni contemporaneamente, il che ne faceva la prima CPU superscalare di Intel – il primo membro superscalare della famiglia x86 sarebbe arrivato solo nel 1993: il Pentium – nonché uno dei pochissimi microprocessori ad avere tale possibilità.

Scheda Hauppauge 4860 (1991). Si tratta di una normale scheda madre 486 AT sulla quale è stato montato un processore i860 a 40 MHz com funzioni di coprocessore matematico ad alte prestazioni. Notare che la scheda è predisposta per ospitare anche una più tradizionale FPU Weitek 4167 (zoccolo vuoto nella parte destra).

Caratteristica tipica dell’i860 era il fatto che si poteva accedere, dal livello del programma in esecuzione, alle singole unità funzionali componenti le tre pipeline del processore; con ciò Intel aveva ottenuto, in modo decisamente originale, uno degli obiettivi dell’architettura RISC e precisamente la semplificazione del microcodice interno della CPU – ma questo aspetto richiedeva la disponibilità di compilatori appositamente studiati e costosi. In più la CPU poteva eseguire la gran parte delle istruzioni floating point in due distinte modalità, scalare e vettoriale: quest’ultima è di fatto una modalità superscalare nella quale il processore esegue fino a tre istruzioni contemporaneamente. Non ultimo, il software compilato per l’i860 risultava molto più lungo rispetto a quello compilato invece ad es. per l’architettura x86, e ciò peggiorava le prestazioni della cache, della memoria ed il rapporto prezzo – prestazioni del sistema nel suo complesso. L’i860 era nondimeno in grado di eseguire programmi appositamente predisposti ed ottimizzati ad una velocità decisamente impressionante per l’epoca, benché quanto sopra esposto ne limitasse in modo sensibile le possibilità d’utilizzo come processore generico. Come risultato di tali contrastanti fattori, le prestazioni dell’i860 erano eccezionali sulla carta ma appena sufficienti (dato il costo) nella realtà. A fronte di circa 60 MFLOPS teorici dichiarati da Intel, se ne potevano ricavare al più 35 - 40 effettivi, nella versione a 50 MHz, ma solamente al prezzo di un’estenuante ottimizzazione manuale del codice; con i compilatori “standard” raramente si superavano i 15 MFLOPS. Quale la ragione di una tale débâcle..? Perché, come ci si rese conto più tardi, la particolare architettura dell’i860 avrebbe richiesto, per funzionare bene, la conoscenza dell’effettivo flusso delle istruzioni (o code path) già durante la fase di compilazione, il che con gli strumenti allora a disposizione sarebbe risultato estremamente difficile già in programmi soltanto un poco complicati; questo processore dava il meglio di sé quando le istruzioni del programma si succedevano l’una dopo l’altra in modo ordinato e regolare, con pochi salti, cosa che è tutto il contrario di quanto normalmente accade nei software d’uso comune. Non bastasse, Intel aveva purtroppo “dimenticato” di provvedere l’i860 di un’efficace gestione del context switching, ovverosia di quel processo col quale, allorché un’interruzione del normale flusso del programma richiede il passaggio ad un’altra parte di quest’ultimo, è necessario salvare i dati contenuti nei registri interni del processore onde poterli in seguito ripristinare allorché si ritorni alla “sequenza principale” del programma stesso. In sua mancanza, l’operazione di “svuotamento” e successivo “ricaricamento” di tutte e tre le pipeline richiedeva fino ad 1/20.000 di secondo, un tempo che se a prima vista può sembrare brevissimo è al contrario un’eternità nel mondo dei microprocessori – cosa che diede il colpo di grazia all’utilizzo dell’i860 come CPU generica.

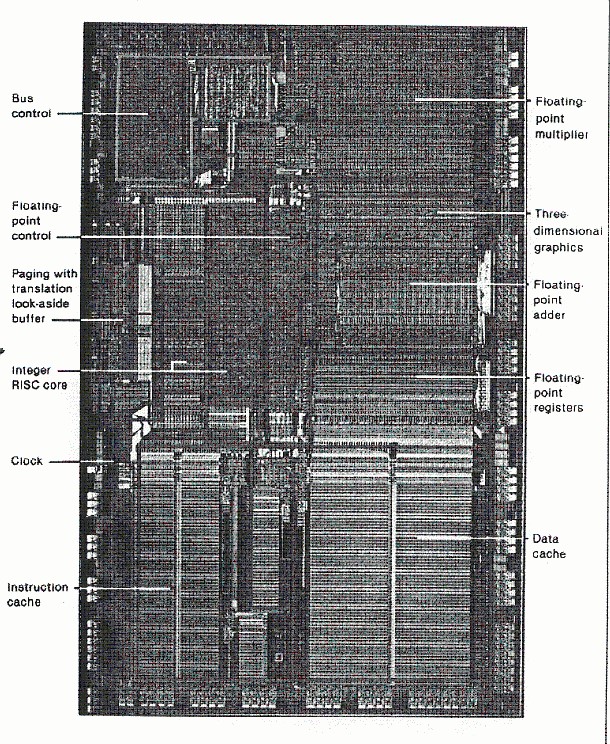

Microfotografia

del chip, o die,

dell’i860

(versione originaria), dimensioni 390

× 495

mil (millesimi di pollice). Nella disposizione delle diverse unità funzionali e

nelle dimensioni si nota una certa rassomiglianza con l’80486,

progettato negli stessi anni e composto da un numero simile di transistor (circa

1,2

milioni). Notare però le cache

separate per dati (8K)

ed istruzioni, 4K,

una caratteristica tipica delle architetture RISC che sarà ripresa nel Pentium

e nei processori successivi (l’i486

aveva al contrario una cache

unificata, anch’essa da 8K,

dimensione ritenuta allora più che sufficiente). La foto, ripresa da una

pubblicazione IEEE del 1991, si riferisce alla prima versione dell’i860

e non alla XP, contenente un numero di transistor più che doppio. L’i860

è contenuto in un package PGA a 262

piedini, contro i 168

dell’80486.

Un

processore di nicchia

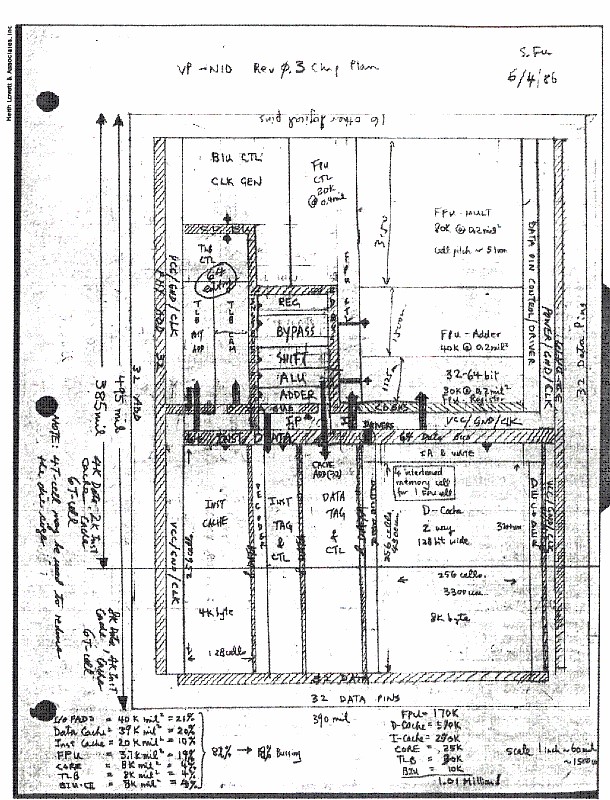

Riprodotto da

una pubblicazione IEEE, schema dell’organizzazione interna del chip i860

(versione originaria con cache da 8K),

che mostra come le sue varie parti siano disposte nel die di silicio e (in basso

a sinistra) quanti transistor siano necessari alla loro realizzazione. Si

osservi come ben il 30%

della superficie e 780K

transistor su circa 1,01

milioni totali siano impegnati dalle memorie cache.

L’i860 venne talvolta utilizzato come “processore grafico”, ad esempio nel NeXT Dimension ed in alcune schede per SPARCStation e DEC 3000. In questo settore però l’esempio più efficace è la Reality Engine di SGI, una soluzione per grafica tridimensionale di alto livello all’interno della quale l’i860 è impiegato nell’unità che si occupa dei calcoli di geometria (GE, o Geometry Engine). Si tratta forse della sua applicazione più diffusa e più facile da incontrare. È altresì documentato il suo utilizzo come “coprocessore matematico” da affiancare di volta in volta ad un i486 su PC oppure ad un membro della famiglia Motorola 68K su Macintosh e, nella versione XR, come processore montato sulle cosiddette schede cluster adapter di prima generazione per sistemi IBM RS/6000. Non dimentichiamo che l’i860 è stato anche impiegato nei supercomputer paralleli Intel iPSC/860, che hanno conosciuto una certa diffusione nell’ambito della ricerca scientifica e le cui schede si trovano talvolta su Ebay ad un prezzo quasi ragionevole. In tutte queste applicazioni l’i860 poteva dare il meglio di sé, ma trattandosi di un processore il cui sviluppo venne ben presto abbandonato da Intel in favore di quello del Pentium, le sue prestazioni furono in breve raggiunte e poi superate da quelle degli altri RISC presenti sulla scena i quali lo “cacciarono” rapidamente dal mercato. L’i860 ha rivestito comunque, è fuor di dubbio, un ruolo importante nello sviluppo dei processori Intel e dei RISC in generale; dai suoi difetti si sono tratte molte utili lezioni messe a frutto nei progetti successivi. Come già detto, la sua architettura è stata una dei motivi ispiratori di MMX; la presenza al suo interno di più pipeline è stata a sua volta un’idea ripresa e migliorata nella gran parte delle CPU attuali.