Il museo in (circa) venti immagini - Short photo tour of UMMR

![]()

Pagina in costruzione

Le immagini in bianco e nero verranno sostituite con versioni a colori

Avvertenza/precisazione n. 1 - Dal momento che più di qualcuno me lo ha chiesto, anche recentemente, ad uso di tutti specifico che sì, molte tra le foto pubblicate in questo sito sono realizzate non con una fotocamera in "modalità macro", bensì semplicemente collocando l'oggetto in un comunissimo scanner piano in formato A4. Contrariamente a quello che tanti pensano, gli scanner per documenti (io uso un HP, ma altre marche vanno egualmente bene), a patto che siano basati su CCD e non su tecnologia CIS (Contact Image Sensor, comune in molti apparecchi Canon) hanno una profondità di campo sufficiente alla scansione di oggetti a modesta tridimensionalità, tipo circuiti integrati, schede ed altri componenti. Il vantaggio rispetto alla "macro" ottenuta con una ordinaria fotocamera digitale - senza entrare nel campo delle vere e proprie, e costose, ottiche macro per reflex tipo l'obiettivo MicroNikkor 60 mm o il 105 mm, che offrono un rapporto di riproduzione reale di 1:1 - è che si ha una distorsione pressoché nulla su tutta l'immagine. In più una scansione a 1200 dpi è già più che adeguata a rilevare particolari anche molto piccoli; salendo a 2400 dpi (non interpolati) si possono riprodurre con facilità particolari appena visibili ad occhio nudo. L'unica avvertenza, fin troppo ovvia in verità, è di fare attenzione a cosa si appoggia sul piano dello scanner e ad interporre eventualmente tra esso e l'oggetto un foglio di plastica trasparente.

Avvertenza/precisazione n. 2 - Ahimè, con la certezza d'attrarre il biasimo dei sostenitori delle enciclopedie cartacee (e dire che io sono un accanito bibliofilo...) le descrizioni dei vari oggetti riportano parecchi collegamenti a pagine dell'amata, odiata, incensata e sbeffeggiata Wikipedia! Non voglio entrare nel merito delle annose, ed a quanto pare sempre vive, polemiche circa l'affidabilità di questa enciclopedia online, da più parti contestata (e da altrettante parti, se non di più, sostenuta). Questa discussione è solo uno degli innumerevoli esempi... Molto probabilmente nel nostro Paese la diffidenza nei confronti di Wikipedia affonda le sue radici in quella, più profonda, verso lo stesso Web. Ognuno è ovviamente libero di formarsi il proprio giudizio e di prendere l'una oppure l'altra posizione. Alla fatidica domanda: "Wikipedia è affidabile oppure no?" bisogna rispondere: dipende dai casi. E' impossibile dare una risposta valida in generale per tutte le sue innumerevoli voci. Molte sono redatte ed aggiornate con competenza, altre invece risultano lacunose, troppo stringate - soprattutto in alcuni campi specifici - o imprecise; una parte infine, la cui consistenza è molto variabile a seconda delle stime e della frequenza di aggiornamento delle pagine incriminate, riporta informazioni errate o parziali (intendo dire "di parte", cioè non neutrali). Riguardo in particolare alla tanto invocata neutralità, è bene ricordare che nemmeno le enciclopedie cartacee sono dei modelli sotto questo punto di vista, specialmente nelle voci di argomento storico e politico. Rimane, incontestabile, il fatto che Wikipedia rappresenti oggi - al di là del significato che si vuole dare alla filosofia di libero contributo ad un'opera collettiva che ne sta alla base, più tecnicamente si parla di user generated content, cioè contenuto generato dagli utenti - una comodissima fonte di riferimento, sempre pronta e di facile accesso. Pur con tutti i suoi limiti, la maggior parte dei suoi articoli è sufficientemente esauriente e precisa per le esigenze dell'utente "medio" ed in parecchi casi anche di chi è più esigente. Ragion per cui, nei casi in cui ho voluto fornire il collegamento alla descrizione di un oggetto, o di una particolare tecnologia, o semplicemente di un termine tecnico, non ho esitato ad inserire il link alla corrispondente pagina di Wikipedia. Con la consapevolezza che, ahimè, nessuno è perfetto, ma tutto è perfettibile - senza censure né crociate ideologiche. Rivolgo comunque a tutti gli utenti di Wikipedia l'invito a leggere con attenzione quanto riportato in questa pagina dell'enciclopedia online. Come si potrà vedere, ho riportato ogniqualvolta necessario ed opportuno uno o più collegamenti a siti ed articoli tecnici più specifici, ed in alcuni casi a testi specialistici. Aggiungo infine che, per quanto riguarda la versione italiana, una buona parte delle voci più tecniche riguardanti l'informatica, l'architettura dei calcolatori elettronici e la tecnologia dei microprocessori è di fatto la semplice traduzione della corrispondente voce inglese, a volte decurtata di alcune parti secondarie.

1) RCA Radechon 6499 (1956, l’esemplare raffigurato risale circa alla metà degli anni Sessanta) - Difficile a credersi secondo gli standard attuali, questa grossa "valvola" che sembra un pezzo di una vecchia telecamera è in realtà una memoria di computer, di tipo elettrostatico (come i cosiddetti "tubi di Williams/Kilburn"). L’RCA Radechon è stato utilizzato per qualche anno negli USA in calcolatori per uso militare che facevano parte del progetto SAGE (rilevamento/tracciatura di missili balistici ed aerei supersonici nemici). La sua capacità di memorizzazione teorica è di circa 16 kbit, quella effettiva di solo 1 kbit a causa dell'interferenza tra bit memorizzati in posizioni adiacenti. Vedi: http://coldwar-c4i.net/SAGE/EE0858-BC.html, oppure per una descrizione più tecnica: http://www.akh.se/tubes/htm/radechon.htm.

Aggiornamento 2 Aprile 2012

L'idea che sta alla base del Radechon venne sviluppata presso i Laboratori Bell (Bell Labs), e non dalla RCA come talvolta si pensa, nel 1952. Dopo il sostanziale fallimento delle memorie elettrostatiche nelle applicazioni puramente digitali, in particolare del costoso tubo Selectron (vedi sotto), si investigò infatti la possibilità di utilizzare questo tipo di memoria in applicazioni miste analogico/digitali o anche solamente analogiche. La Westinghouse fu il primo costruttore ad intraprendere questa strada ed introdusse, nella prima metà degli anni Cinquanta, due tubi molto simili al Radechon, noti con le sigle 7225 e 7566, oltre a versioni speciali non commerciali (WX-4052, 4064 e 4065). Il Radechon (6499), elaborazione migliorata dell'originaria idea dei Bell Labs, venne commercializzato dalla RCA a partire dal 1956 per circa un decennio. La caratteristica che lo distingueva dai prodotti della concorrenza era la capacità di memorizzare diversi livelli di carica, il che lo rendeva a tutti gli effetti una memoria per dati analogici. Anche la Raytheon sviluppò una propria versione di questo tubo, messa in commercio con la sigla QK357. Ad essa ne seguirono altre sviluppate espressamente per applicazioni militari (radar): la QK464A o 6835, la CK7570 (QK411A) e la CK7571 (QK685), quest'ultima fabbricata anche da Fairchild/Dumont. La struttura del Radechon ispirò in Unione Sovietica progetti quasi identici, in particolare i tubi della serie IN (o LN, a seconda della traslitterazione dal cirillico), oggigiorno meno rari del Radechon e dunque meno costosi per i collezionisti. Come memoria digitale il tubo Radechon è stato impiegato nel calcolatore sperimentale Model 1 della Rice University (1958, vedi http://www.cs.rice.edu/History/R1/).

I tubi Radechon sono difficili, ma non impossibili da trovare (su Ebay o altrove). Quella che segue è una lista aggiornata di siti che parlano, più o meno diffusamente, di questo interessante tipo di memoria.

Scansione della pagina dedicata al 6499 nel catalogo RCA: http://www.nixiebunny.com/radechon.pdf.

Ottima scansione del datasheet originale RCA: http://www.bitsavers.org/pdf/rca/storage_tubes/6499_Radecon_Mar56.pdf.

Anche: http://www.akh.se/tubes/htm/6499.htm.

Pagina con immagini **molto** dettagliate: http://www.decadecounter.com/vta/articleview.php?item=795.

Pagina con 3 immagini (il nome del tubo è riportato erroneamente): http://www.dvq.com/oldcomp/misc.htm.

Pagina con 3 belle immagini, benché senza descrizione tecnica: http://tubetime.us/?p=25.

Tubo simile al Radechon, probabilmente fabbricato da Raytheon: http://g4oep.atspace.com/radechon/radechon.htm.

Breve storia delle memorie elettrostatiche

Nel periodo iniziale dello sviluppo dei calcolatori elettronici (anni Quaranta) la realizzazione di memorie con capacità e velocità accettabili poneva una serie di problemi la cui soluzione era tutt'altro che facile. Tra essi il più importante riguardava il numero di componenti richiesti per la realizzazione di una data quantità di memoria: era quella infatti l'epoca delle "valvole" o tubi elettronici, dispositivi costosi, ingombranti e poco affidabili. Utilizzando come unità basilare per una memoria il flip-flop, che è un circuito elettronico bistabile (cioè con due stati stabili, che possono essere impiegati per "memorizzare" uno zero e rispettivamente un 1), per ciascun bit memorizzato occorrono almeno due singoli triodi ovvero un doppio triodo. Al crescere della capacità della memoria il numero di valvole richiesto diventa rapidamente insostenibile sia da un punto di vista economico che da quello dell'energia assorbita per l'alimentazione. Una delle prime tecnologie praticamente utilizzabili sviluppate per la realizzazione di memorie (in particolare di RAM) nei calcolatori elettronici di prima generazione è stata quella dei cosiddetti "electrostatic storage tubes", derivati dai comuni tubi a raggi catodici impiegati nei televisori dell'epoca. Il principale rappresentante di questa famiglia di primitive memorie per computer è stato il tubo di Williams-Kilburn, sviluppato tra il 1946 ed il 1947 da F. Williams e T. Kilburn dell'Università di Manchester. Come la maggior parte delle memorie di questo tipo, esso utilizza il principio dell'emissione secondaria di elettroni. Quando un punto viene "scritto" sullo schermo di un tubo a raggi catodici, l'area del punto acquista una piccola carica positiva, mentre la zona immediatamente circostante si carica negativamente. Questa situazione dura per qualche istante (pochi millisecondi) dopo la "scrittura" e può essere sfruttata per memorizzare un bit di informazione. La lettura, che comporta la distruzione dell'informazione memorizzata (e ne richiede dunque la ri-scrittura), si ottiene in maniera simile alla scrittura, con un fascio di elettroni che colpisce i vari punti dello schermo del tubo. Quelli in cui era stato precedentemente scritto un "1", e che dunque sono caricati positivamente, generano un debole impulso di corrente che viene rilevato da una maglia metallica fine collegata allo schermo del tubo, ovvero formante lo schermo stesso. La rapida dispersione della carica dei punti "memorizzati" richiede il loro periodico rinfresco, in maniera simile a quanto avviene nelle attuali DRAM (come queste ultime, il tubo di Williams-Kilburn utilizza la capacità elettrica per memorizzare bit di dati). La capacità di memorizzazione di un tubo di Williams-Kilburn era di circa 1 kbit. Questo tipo di memorie furono utilizzate con successo, nonostante i loro molti problemi (in primo luogo l'inaffidabilità) in svariati calcolatori elettronici, anche commerciali, della prima generazione quali il Manchester Mark I (commercializzato come Ferranti Mark I), la Macchina IAS, l'UNIVAC 1103, gli IBM 701 e 702, lo SWAC ed infine il primo calcolatore elettronico prodotto in serie nell'allora Unione Sovietica, lo Strela-1 (1953). Il Radechon di RCA è anch'esso un componente di questo tipo. Sul principio dell'emissione secondaria di elettroni si basava anche il tubo RCA Selectron (vedi), il quale però ha una struttura completamente diversa sia dal tubo di Williams-Kilburn che dal Radechon. Verso la metà degli anni Cinquanta le memorie elettrostatiche furono completamente soppiantate da quelle magnetiche (a nuclei o di altro tipo).

Siti con esemplari di Radechon: http://www.dvq.com/oldcomp/misc.htm; http://www.tubecollector.org/6499.htm (eccellente sito, immagini molto dettagliate); http://www.nixiebunny.com e http://www.nixiebunny.com/radechon.pdf (scansione di data-book RCA).

Interessante serie di immagini, molto chiare: http://www.flickr.com/photos/tubetime/3436015144/; in questa pagina lo stesso collezionista fornisce qualche informazione in più: http://tubetime.us/?cat=10.

Interessanti note storiche sullo sviluppo del Radechon: http://www.davidsarnoff.org/kil-chapter10.html.

Burroughs BD-311: è un "beam switching tube", un tipo particolare di valvola impiegata negli anni Cinquanta e Sessanta nei circuiti di conteggio (decimali) di calcolatori ed altre apparecchiature elettroniche.

Vedi: http://www.decadecounter.com/vta/articleview.php?item=455; http://www.decadecounter.com/vta/articleview.php?item=268.

Descrizione del funzionamento: http://www.electricstuff.co.uk/beamswitch.html.

Anche: http://www.youtube.com/watch?v=E4VCOOMfzvI (è proprio vero, su YouTube c'è di tutto!)

Vedi anche: http://en.wikipedia.org/wiki/Nixie_tube (parla anche del beam switching tube).

2) Modulo a "valvola" di computer IBM 603/604 Electronic Calculating Punch (1948, l'esemplare è del 1953) - Questo è uno tra le centinaia di moduli costituenti la CPU di un calcolatore IBM 604. Si di una macchina programmabile per eseguire ad alta velocità operazioni aritmetiche su dati letti da schede perforate. Tutta la parte elettronica era realizzata con moduli logici elementari a valvole simili a quello raffigurato qui sopra. Il 604 è stato tra i primissimi computer elettronici ad avere una certa diffusione commerciale. Si trovano in rete molti materiali che lo riguardano; vedi ad es.: http://en.wikipedia.org/wiki/IBM_604, oppure http://www.columbia.edu/acis/history/604.html. Una descrizione dettagliata della macchina si trova in: http://ed-thelen.org/comp-hist/IBM-604.html.

Vedi: http://www.decadecounter.com/vta/tubepage.php?item=38&user=0.

L'IBM 603 Electronic Multiplier ( http://www.columbia.edu/acis/history/603.html) è storicamente importante perché è stato la prima macchina calcolatrice elettronica programmabile prodotta su larga scala; venne utilizzata come unità logico/aritmetica nel calcolatore SSEC (Selective Sequence Electronic Calculator). Il modello 604 è una sua evoluzione più veloce e complessa (con clock a 50 kHz contro i 35 del modello 603). Entrambe queste macchine possono essere considerate precursori dei primi veri e propri computer IBM quali il modello 701.

3) Scheda a transistor di calcolatore CDC (circa 1965) - Com’erano

costruiti i calcolatori prima dell’avvento dei circuiti integrati e dei

microprocessori…? La risposta è semplice: con

migliaia di componenti a bassa densità disposti su decine o centinaia di schede.

Qui sopra vediamo un doppio flip-flop (elemento base di un registro) appartenuto

ad una macchina CDC (1964). Gli oggetti di forma rotonda sono transistor

singoli. Le dimensioni della scheda sono (circa) 8 x 4 cm.

4) Scheda IBM SMS (circa

1965) - Nel 1958, nell’ambito del progetto STRETCH o IBM 7030

(vedi, uno dei

primissimi supercalcolatori, sviluppato su richiesta del Livermore Radiation

Laboratory dell’Università della California ed in particolare del suo

direttore Edward Teller, noto per essere stato "il padre della bomba

H", che voleva avere a disposizione un computer in grado di risolvere in

tempi ragionevoli i complessi problemi di fluidodinamica correlati alle fasi

immediatamente successive allo scoppio degli ordigni termonucleari), venne

adottata la tecnologia SMS o Standard Modular System, un sistema di schede a

transistor standardizzate usato fra l’altro nelle macchine IBM delle serie 70xx, 1400 (1960) e 1620 (1959). SMS è

stato tra i primi esempi di standardizzazione tecnologica a livello hardware nel

settore dell’informatica (anche se limitato ad un unico costruttore,

IBM).

US Patent 3.008.113, 1958 (PDF, 686

KB): ![]()

5) Memoria a nuclei magnetici Microdata (1976) - Affermatasi durante gli anni Sessanta, la tecnologia delle memorie a nuclei magnetici (o nuclei di ferrite) si affermò come uno standard di fatto fino alla diffusione delle memorie a circuito integrato. Tutti i minicomputer "classici" tra cui i DEC PDP 8, 10 ed 11, i Data General NOVA e così via hanno fatto uso di questo tipo di memoria. La memoria a nuclei era certamente un miglioramento rispetto ai costosi e poco affidabili tipi di RAM impiegati prima del suo avvento, ma la sua densità ed i tempi d’accesso medi non sono neppure lontanamente paragonabili con quelli ottenibili utilizzando i circuiti integrati. La scheda raffigurata qui, le cui dimensioni sono di circa 35 x 25 cm, ha una capacità di 8 KByte.

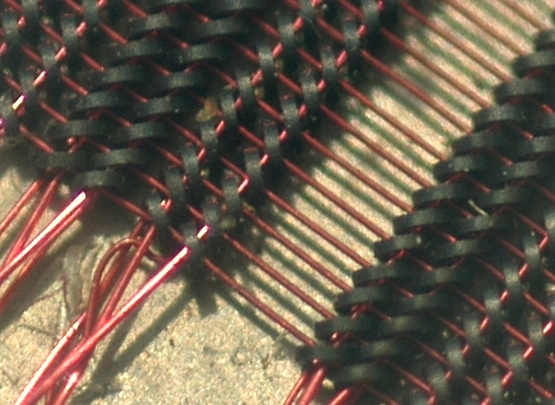

Vista ravvicinata di una memoria a nuclei magnetici. L’immagine copre un area di circa 1,5 x 1,2 cm ed è stata ottenuta con la funzione "macro" della fotocamera digitale Nikon Coolpix 5000. Si nota come ciascun nucleo sia attraversato da 3 fili: due linee di controllo X ed Y incrociate a formare un angolo di 90° ed una terza linea di lettura (sense line). Vedi questa immagine. Questa memoria apparteneva ad un NCR Electronic Cash Register mod. 230 (vedi questa pagina per l'immagine della scheda completa: http://www.thecorememory.com/html/electronic_boards.html).

Dettaglio di una memoria a nuclei DEC da 16 KB (1975). I singoli nuclei hanno un diametro di circa 15 mil (millesimi di pollice). Questa immagine è stata ottenuta con un obiettivo MicroNikkor 60 mm f 2,8 su fotocamera Nikon D100.

Breve storia delle memorie a nuclei magnetici

La memoria a nuclei magnetici (Magnetic Core Memory, MCM) ha rappresentato per circa un quarto di secolo, fino all'avvento delle memorie a circuito integrato, la principale ed in molti casi l'unica tecnologia praticamente disponibile per la realizzazione delle RAM nei calcolatori elettronici. Il primo brevetto relativo a questo tipo di dispositivo fu ottenuto nel 1947 dall'americano Frederick Viehe, che aveva sviluppato un primitivo prototipo di memoria a nuclei nel proprio laboratorio. Allo sviluppo della tecnologia dei nuclei magnetici lavoravano in quegli stessi anni due fisici statunitensi di origine cinese, An Wang e Way Dong Woo, che nel 1949 presentarono un dispositivo chiamato "pulse transfer controlling device", un circuito progettato per l'impiego come commutatore di corrente in sistemi elettromeccanici. Wang e Woo lavoravano entrambi presso i Computer Laboratories dell'Università di Harvard, che non era interessata allo sfruttamento commerciale delle invenzioni dei propri collaboratori. Wang potè così richiedere il brevetto per il dispositivo inventato assieme al collega. Del loro lavoro venne a conoscenza, tramite le pubblicazioni scientifiche dell'epoca, il gruppo di lavoro guidato da Jay Forrester, che al MIT si occupava della realizzazione del calcolatore elettronico Whirlwind. Questa macchina, che avrebbe dovuto essere impiegata per complessi calcoli in tempo reale, richiedeva una RAM veloce e di discreta capacità: inizialmente si pensò di utilizzare i cosiddetti "tubi di Williams-Kilburn", una forma di memoria elettrostatica basata su tubi catodici; tale soluzione, però, era costosa e poco affidabile. Forrester quindi contattò Wang ed insieme a quest'ultimo sviluppò nel 1951 due importanti innovazioni che furono alla base dell'impiego dei nuclei magnetici come elementi di memoria nei computer digitali: 1) il meccanismo di lettura/scrittura (chiamato "write after read cycle") che risolveva il problema di come leggere una memoria la cui lettura comportava la cancellazione dei dati contenuti e 2) il controllo a correnti coincidenti (coincident current control system, vedi http://ed-thelen.org/comp-hist/Byte/76jul.html) grazie al quale un gran numero di nuclei poteva essere "comandato" da pochi fili. L'invenzione 1) si deve a Wang e la 2) a Forrester. Quest'ultima richiedeva il passaggio attraverso i nuclei di uno dei fili con un angolo di 45°, ciò che rendeva di fatto impossibile la fabbricazione a macchina delle memorie a nuclei: per molti anni esse furono infatti assemblate manualmente (!) con l'aiuto di microscopi e micro-manipolatori (lavoro davvero poco invidiabile). Wang non ottenne il brevetti per le sue invenzioni fino al 1956, quando già diversi fabbricanti impiegavano su larga scala la memoria a nuclei. Ne derivò una lunga serie di cause civili alla fine delle quali IBM versò a Wang una cospicua somma di denaro (svariati milioni di Dollari dell'epoca) in cambio dei diritti di sfruttamento delle sue scoperte. Tali fondi vennero successivamente utilizzati da Wang per l'ampliamento dei Wang Laboratories, una società da lui fondata che divenne protagonista di primo piano nel settore dell'informatica. Le prime unità di memoria a nuclei magnetici per uso commerciale vennero prodotte attorno alla metà degli anni Cinquanta. Successivamente, soprattutto in Estremo Oriente (Giappone, Corea, Taiwan) furono impiantate numerose fabbriche dedicate unicamente alla produzione (manuale o nel migliore dei casi semiautomatica) di memorie a nuclei, il cui prezzo calò rapidamente trasformando questa tecnologia nella prima scelta in fatto di RAM per calcolatori elettronici, posizione che mantenne fino all'arrivo, nella prima metà degli anni Settanta, delle prime DRAM a circuito integrato. Le memorie a nuclei magnetici sono state prodotte su scala industriale fino all'inizio degli anni Ottanta.

La memoria a nuclei magnetici è una RAM non volatile (l'informazione registrata non si perde se viene a mancare l'alimentazione elettrica) a lettura distruttiva (la lettura dell'informazione registrata comporta la sua cancellazione); inoltre, questo tipo di memoria è poco sensibile all'influsso degli impulsi elettromagnetici (EMP), il che ne ha garantito per anni l'impiego in molte applicazioni aerospaziali, militari e di controllo industriale. A differenza delle memorie a semiconduttore (MOS oppure bipolari) la memoria a nuclei magnetici basa il suo funzionamento, dunque il "passaggio" dallo stato 0 all'1 e viceversa, su specifici valori di corrente anziché di tensione. Infine, le memorie a nuclei magnetici sono sensibili alla temperatura di funzionamento (perché le caratteristiche di isteresi dei nuclei variano con la temperatura stessa) e, contrariamente alle memorie a circuito integrato, richiedono riscaldamento anziché raffreddamento. I principali limiti delle memorie a nuclei sono la scarsa velocità (1,2 microsecondi il tempo medio di ciclo delle MCM di prima generazione, scesi fino a 600/650 ns verso la fine degli anni Settanta), parecchie volte inferiore a quella dei dispositivi a circuito integrato, il notevole ingombro (una tipica scheda MCM contiene non più di 64 KB) dovuto all'impossibilità di manipolare nuclei troppo piccoli e l'elevato prezzo per bit.

Vedi: http://www.technikum29.de/en/computer/storage-media#core-memory.

Anche: http://infolab.stanford.edu/pub/voy/museum/pictures/display/2-1.htm.

Un altro tipo di memoria utilizzato agli albori dell’informatica e rimasto in uso in certe applicazioni (ad es. calcolatrici elettroniche e buffer per terminali) fino agli anni Settanta è la memoria a linea di ritardo (delay line memory). Qui sopra si vedono due esemplari fabbricati da Olivetti (vedi), la cui capacità di memorizzazione è di circa 1 kbit. Questo tipo di memorie, in genere cicliche (nel senso che i dati in uscita se non utilizzati in qualche fase dell’elaborazione sono ritrasmessi all’ingresso del dispositivo, e così via indefinitamente) sfrutta la trasformazione di segnali elettrici in impulsi di natura meccanica (e viceversa), ad esempio acustici, che vengono trasmessi attraverso un opportuno materiale sfruttandone la velocità di propagazione all’interno di quest’ultimo per "memorizzarli" durante il tempo che essi impiegano ad attraversarlo. Le memorie a linea di ritardo più recenti sfruttano invece il fenomeno della magnetostrizione cioè della capacità di alcuni materiali ferromagnetici di cambiare le loro dimensioni a seguito dell’applicazione di un campo magnetico. In questo secondo tipo di memorie gli impulsi sono trasmessi all’interno della memoria stessa e dunque memorizzati sotto forma di onde successive di contrazione/rilassamento di un filo metallico indotte dall’applicazione ad una sua estremità del campo magnetico generato da un induttore. All’altro capo del filo un trasduttore trasforma tali onde in impulsi elettrici (fase di "lettura" della memoria). Le prime memorie a linea di ritardo impiegate in calcolatori elettronici erano di tipo acustico e vennero introdotte nella seconda metà degli anni Quaranta da J. Presper Eckert per l'impiego nei computer EDVAC, EDSAC e UNIVAC-I. In questo tipo di linee di ritardo si sfrutta il tempo di propagazione di un impulso acustico all'interno di un mezzo opportuno, in genere mercurio mantenuto ad una temperatura di circa 40°. Realizzare memorie del genere era difficile e poneva una serie di problemi complessi, in primo luogo la necessità di evitare riflessioni indesiderate degli impulsi acustici e di disporre di trasduttori di "lettura" sufficientemente precisi. La capacità di memoria delle linee di ritardo impiegate nell'EDSAC era di circa 600 bit. Le linee di ritardo a magnetostrizione, più semplici, compatte ed efficienti, furono utilizzate come memorie per calcolatori elettronici (LEO-I, alcuni computer Ferranti degli anni Cinquanta) per un periodo di tempo limitato, a causa dell'affermarsi della tecnologia delle memorie a nuclei magnetici. Ebbero invece più fortuna come memorie per calcolatrici elettroniche da tavolo (es. l'Olivetti Programma 101 ed altre macchine da essa derivate, la serie Monroe EPIC) e per video-terminali.

Vedi: http://www.vintagecalculators.com/html/calculator_memory_technologies.html.

Anche: http://www.decodesystems.com/delay-line-memory.html; http://www.technikum29.de/en/computer/storage-media.

Scheda RAM da 64 KB per IBM System/23 "Datamaster" (1981). I chip della RAM, di fabbricazione Texas Instruments con marcatura IBM, sono sovrapposti (stacked) a gruppi di due. Il rapido sviluppo delle tecnologie LSI/VLSI durante gli anni Settanta ha fatto sì che nel giro di poco tempo le RAM a circuito integrato MOS soppiantassero tutti gli altri tipi di memoria, in modo particolare quello a nuclei magnetici (sopra) e quello a bolle magnetiche (sotto). Alla metà degli anni Ottanta la quasi totalità delle RAM commercializzate era ormai realizzata con circuiti integrati.

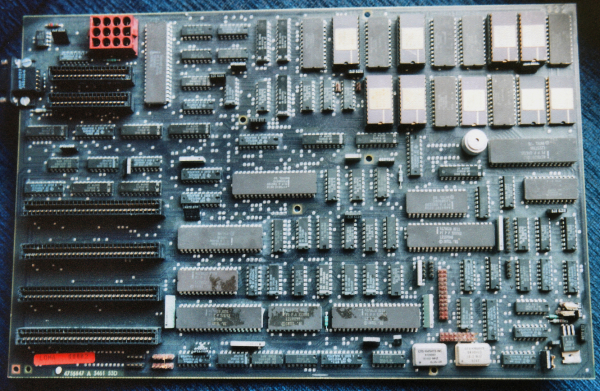

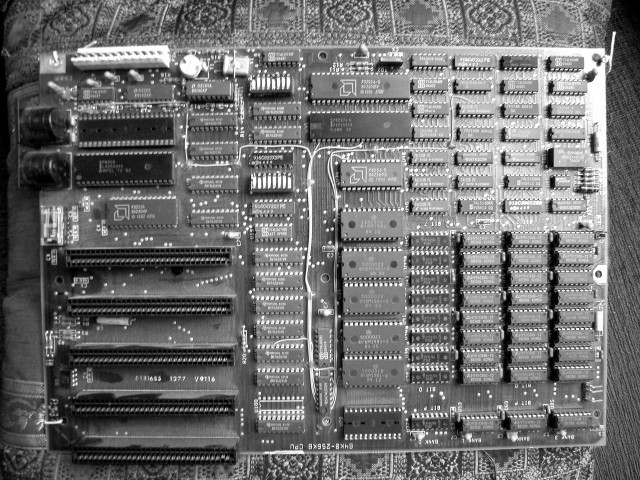

L'IBM Datamaster (qui sopra la "scheda madre" - notare che gli integrati hanno tutti sigle IBM), conosciuto anche come "System/23" (IBM model 5322, http://www-03.ibm.com/ibm/history/exhibits/pc/pc_9.html) venne annunciato nel Luglio 1981, un mese prima del PC originale. Si tratta di una macchina "all-in-one" basata su CPU Intel 8085, memoria RAM compresa tra 64 e 256 KB (che potevano essere gestiti dal processore tramite un'apposita logica di bank-switching), due floppy disk da 8 pollici la possibilità di collegare un disco rigido esterno. Il Datamaster venne concepito per essere un sistema rapido da installare e semplice da adoperare, rivolto in primo luogo agli applicativi gestionali ed all'elaborazione di testi. E' possibile che l'esperienza maturata da IBM durante il suo sviluppo con la CPU 8085 abbia contribuito a spingere la stessa IBM verso la scelta dell'Intel 8088 in luogo di altri microprocessori a 16 bit come CPU per il PC originale.

Vedi: http://oldcomputers.net/ibm5322.html; http://en.wikipedia.org/wiki/IBM_System/23.

Anche: http://www.flickr.com/photos/mwichary/2282600489/.

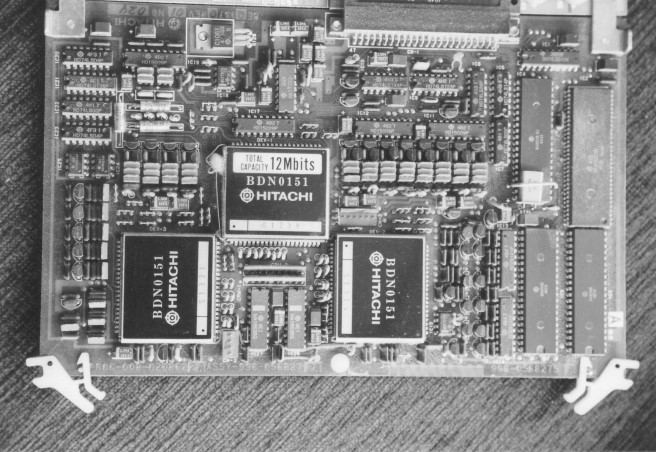

6) Memoria a bolle magnetiche Hitachi (1985) - La memoria a bolle magnetiche (o MBM, acronimo del corrispondente in lingua inglese Magnetic Bubble Memory) è un particolare tipo di memoria non volatile nella quale l’informazione è registrata in forma di piccole aree magnetizzate (chiamate appunto "bolle") formate in una lamina sottile (thin film) di particolari leghe metalliche. Questo tipo di memoria, che è corretto classificare come "memoria di massa" piuttosto che come tecnologia per memorie RAM sembrò estremamente promettente lungo tutti gli anni Settanta, allorché le principali aziende del settore decisero di investire nel suo sviluppo, ma cadde rapidamente nell’oblio intorno alla metà del decennio successivo, allorché si ebbe il primo grande crollo del prezzo al MB dei dischi rigidi. La MBM è in larga misura il frutto dell’inventiva e del lavoro di ricerca di un’unica persona: Andrew Bobek, che già aveva lavorato anni prima allo sviluppo delle memorie a nuclei magnetici ed alla creazione del Twistor, un tipo di memoria basato sul fenomeno della magnetostrizione (come le memorie a linea di ritardo magnetostrittiva, che ebbero ad es. una certa diffusione nelle prime calcolatrici elettroniche da tavolo).Negli anni Cinquanta, con lo sviluppo delle leghe ferroelettriche avanzate tra cui il "Terfenol D" (una lega di Ferro, Terbio e Disprosio sviluppata dai laboratori di ricerca della Marina militare USA o NOL, "Naval Ordnance Laboratories" da cui il nome), si cominciò a pensare di utilizzare questo fenomeno per memorizzare dati binari all’interno di linee di ritardo, ovverosia dispositivi nei quali si sfrutta il tempo di propagazione al loro interno di un impulso applicato all’estremità, nel senso che mentre l’impulso medesimo "viaggia" all’interno della linea, è "memorizzato" in essa. Le linee di ritardo a magnetostrizione immagazzinano i singoli bit come onde successive di contrazione/rilassamento del materiale indotte, per l’appunto, dall’applicazione di un opportuno campo magnetico ad un filo di Terfenol o altra lega similare. Il Twistor (circa 1967) è un’evoluzione di questo concetto, nella quale i bit sono memorizzati in un nastro di materiale ferromagnetico avvolto (twisted) attorno a conduttori elettrici che servono per la lettura dei dati (in modo simile a quanto accade nelle memorie a nuclei magnetici) e magnetizzato da appositi elettromagneti posti alle sue estremità. Per qualche tempo questo sembrò un tipo di memoria molto promettente, perché a differenza delle memorie a nuclei magnetici – con le quali condivideva la caratteristica d’essere non volatile, di mantenere cioè intatto il suo contenuto anche dopo che l’alimentazione elettrica fosse stata tolta – poteva essere assemblato in modo completamente automatico (il montaggio delle migliaia e migliaia di minuscoli anellini di ferrite costituenti le MCM richiedeva comunque il lavoro al microscopio di abilissimi operai specializzati, spesso ragazze) ed era più semplice, dunque più affidabile; nonostante ciò, dovette scontare l’enorme popolarità raggiunta dai dispositivi MCM e, successivamente, la rapidissima crescita delle memorie a semiconduttore – che fecero letteralmente piazza pulita di tutte le tecnologie concorrenti. Il Twistor, sviluppato in gran parte dai Laboratori Bell (Bell Labs) venne impiegato solamente in pochi sistemi, perlopiù destinati ad usi militari come il calcolatore di governo del missile Nike X, oppure nei computer di controllo dei primi commutatori telefonici elettronici della stessa Bell/AT&T, segnatamente l’1ESS ed i successori, fino al 4ESS (circa 1975). La memoria a bolle magnetiche nasce da un’intuizione di Bobek, giunto ai Laboratori Bell nel 1967, tesa a migliorare l’idea di base del Twistor. Egli pensò che, se fosse stato possibile trovare un materiale nel quale le zone magnetizzate o "domini magnetici", rappresentanti ciascuna un singolo bit d’informazione, si muovessero prevalentemente in una specifica direzione, sarebbe stato possibile sostituire il nastro ferromagnetico del Twistor con un’intera lamina sottile di tale materiale, aumentando dunque sensibilmente la densità d’informazione della memoria così ottenuta. La prima lega sulla quale Bobek lavorò fu l’ortoferrite (OFE); egli scoprì in che quest’ultima, in opportune condizioni (con l’applicazione cioè di un campo magnetico esterno sufficientemente potente), i domini magnetici tendevano ad assumere dimensioni puntiformi, simili a bolle, consentendo di immagazzinare parecchi dati binari in una superficie ristretta. A questo punto cominciò la ricerca di un materiale ancora più adatto dell’ortoferrite, che venne individuato nel granato almandino, un minerale che è sostanzialmente un particolare tipo di silicato di Ferro. Per garantire un regolare movimento delle bolle magnetiche da un’estremità all’altra della memoria si pensò di depositare un apposito "percorso" formato da piccole guide di materiale ferromagnetico sulla superficie del granato, percorso che le bolle avrebbero seguito grazie ad una periodica inversione del campo destinato alla magnetizzazione delle guide stesse. Lo sviluppo delle memorie MBM nei Bell Labs passò attraverso almeno quattro distinte scoperte fondamentali: il moto controllato dei domini magnetici in un materiale bidimensionale; l’applicazione dell’ortoferrite nella realizzazione delle "guide" preposte a controllare il movimento delle bolle magnetiche; la scoperta della forma cilindrica stabile dei domini magnetici (bolle); l’impiego del granato come substrato sul quale viene deposto un film di materiale magnetico in cui avviene la formazione dei domini magnetici. Nel Settembre 1974 comparve il primo importante articolo sulle memorie MBM, che valse un premio al suo autore (H.E.D. Scovil, sempre dei Bell Labs).

Modulo di memoria MBM Texas Instruments TIB S0004-3 con capacità di 11,48 KB (1981, vedi).

Nella loro forma definitiva, le MBM sono memorie non volatili e "cicliche", nel senso che i dati scritti in esse in un dato momento si muovono al loro interno fino a raggiungere, ad un’estremità, dei rivelatori che li leggono e li rimandano all’altro capo della memoria stessa; questo ciclo si ripete finché sia necessario mantenere memorizzato il dato medesimo. La scrittura della MBM è ottenuta mediante minuscoli elettromagneti posti ad una delle sue estremità, ciascuno in corrispondenza di un’immaginaria "linea" corrispondente concettualmente ad un Twistor a sviluppo lineare; un campo magnetico perpendicolare al foglio di granato assicura la formazione dei domini magnetici a forma di bolla. Quando vennero ideate, le MBM avevano diversi vantaggi rispetto ai dischi rigidi: innanzitutto, non necessitavano di parti in movimento, quindi consumavano poco ed erano piccole e non rumorose; in secondo luogo, consentivano una notevole densità d’immagazzinamento delle informazioni. Il loro principale limite consisteva nella bassa velocità, perché le informazioni contenute dovevano attraversare tutta la memoria (nel ciclo sopra descritto) prima di poter essere lette; per questo motivo le MBM sono considerate memorie "a scorrimento" (shift). Nel 1975 il team di Bobek creò una MBM dimostrativa da 4 Kbit ampia 1 centimetro quadrato, che destò immediatamente grande interesse. Nel giro di pochi mesi le “bolle” erano sulla bocca di tutti gli esperti del settore, che pronosticavano loro un luminoso futuro nel quale sarebbero state capaci di sostituire sia le tradizionali RAM a nuclei magnetici che i dischi ed anche i neonati floppy disk. A partire dal 1976 praticamente tutti i grandi nomi dell’informatica conducevano ricerche nel campo delle MBM: vennero presentati modelli da 1 Mbit (vedi Intel 7110) ed anche più grandi, fino a 4 Mbit. Tuttavia, nonostante tutto l’interesse suscitato dal loro apparire sulla scena, le MBM ebbero uno scarso successo commerciale (dovuto principalmente al costo, mediamente elevato) e rimasero un prodotto di nicchia, dedicato ad applicazioni particolari in cui i dischi non avrebbero potuto tornare utili. Il crollo dei prezzi dei dischi rigidi seguito all’introduzione sul mercato del Seagate ST506, primo Winchester da 5,25’’, le escluse rapidamente dalla competizione, tanto che nel 1984 soltanto Texas Instruments e pochissimi altri continuavano a produrre moduli MBM. Tra le rare applicazioni commerciali delle MBM ricordiamo il computer PC 5000 di Sharp e la console Bubble System di Konami (1984).

Vedi: http://www.decadecounter.com/vta/tubepage.php?item=30&user=0.

Primo microprocessore single chip commerciale - First single chip commercial microprocessor

7) Microprocessore Intel 4004 (1971) - Introdotto il 15 Novembre 1971 col profetico slogan "announcing a new era in integrated electronics", l’Intel 4004 è considerato da molti il primo microprocessore della storia. E’ stato sviluppato nell’ambito di una collaborazione tra la Intel (che era allora un produttore di memorie) e la casa giapponese Busicom, per essere impiegato nei calcolatori da tavolo fabbricati da quest’ultima. In particolare allo sviluppo del 4004 hanno concorso tre persone: Federico Faggin (capo- progetto), Ted Hoff (che ne ha proposto nel 1969 le linee generali dell’architettura di sistema) e Masatoshi Shima della Busicom. Realizzato con tecnologia PMOS a 10 micron, contiene circa 2.300 transistor e funziona ad una frequenza massima di 740 kHz. Il 4004 è una CPU a 4 bit che può eseguire circa 90.000 istruzioni al secondo ed impiega un’architettura di sistema di tipo Harvard (con memorie dei dati e del programma separate) a singolo bus. Benché rudimentale secondo gli attuali standard in fatto di microprocessori, il 4004 (venduto unitamente ad un set di circuiti di supporto col nome di Intel MCS-4) attirò da subito grandi attenzioni da parte dell’industria e diede il via all’esplosiva crescita del mercato dei microprocessori. Oggi i processori 4004 sono oggetti molto ricercati dai collezionisti. Una descrizione concisa ma completa e chiara del 4004 è disponibile in Wikipedia: http://en.wikipedia.org/wiki/4004, assieme ad una serie di collegamenti interessanti per chi cerca approfondimenti e notizie tecniche.

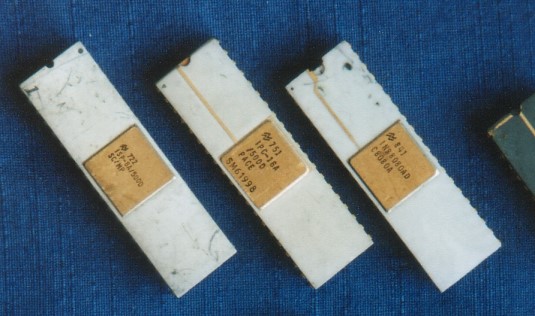

Tre "antichi" processori fabbricati da National Semiconductors (vedi): a sinistra l’SC/MP o ISP-8A/500D a 8 bit (introdotto nel 1974); al centro, il PACE o IPC-16A/500D (16 bit, 1975) ed infine a destra una versione dell’8080, la INS8080AD. L’SC/MP è stato il primo microprocessore a consentire un effettivo multiprocessing con due o più CPU; il PACE, uno dei primissimi microprocessori a 16 bit, deriva direttamente dall’architettura dei minicomputer NOVA di Data General.

http://www.chipdocs.com/datasheets/datasheet-pdf/National-Semiconductor/INS8060.html

http://www.cpu-world.com/CPUs/SC-MP_II/

http://www.dos4ever.com/SCMP/SCMP.html

http://userwww.sfsu.edu/~hl/c.SC-MP.html

http://members.aol.com/mk14emu/scmp.htm

http://burks.brighton.ac.uk/burks/foldoc/96/102.htm

http://www.cpu-world.com/forum/viewtopic.php?t=9469

http://www.chipdb.org/img-national-semiconductor-ipc-16a-_500d---pace-white-6395.htm

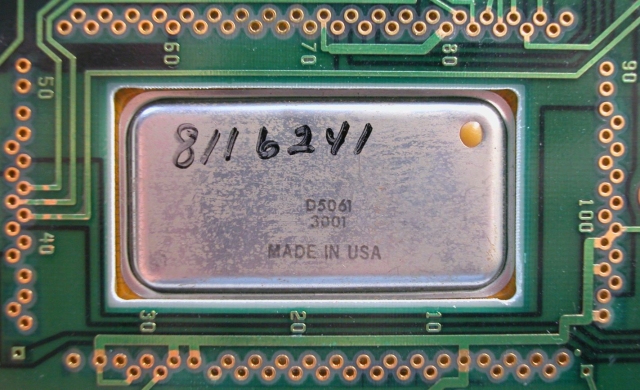

http://en.wikipedia.org/wiki/IMP-16

8) Microprocessore HP BPC D5061-3001 (questo es.: 1984) - Il processore BPC di Hewlett Packard, il cui primo prototipo venne sviluppato negli anni Settanta (1972/3), è da taluni considerato il primo microprocessore single-chip a 16 bit (altri ritengono invece che questo sia stato il TMS9900 di Texas Instruments). BPC è stato tuttavia senza dubbio il primo microprocessore microprogrammato ed una delle primissime CPU NMOS commercializzate. Questo processore ha trovato impiego solamente in macchine HP come ad esempio il computer 9845, l’analizzatore di spettro 3585A ed il sistema di sviluppo 64000. E’ contenuto in un particolare package ceramico a 82 contatti. Fisicamente è un circuito integrato ibrido contenente più chip (3) e precisamente l’ALU, la FPU e l’unità di I/O, che complessivamente integrano circa 18.000 transistor. La versione -3001 è stata progettata per l’impiego nell’HP 9845 e contiene un ulteriore integrato per la gestione della memoria (AEC, Address Extension Chip): vedi per una descrizione il numero 1976-6 dell’HP Technical Journal: http://www.hpl.hp.com/hpjournal/pdfs/IssuePDFs/. Il BPC era fabbricato con processo NMOS-II.

Vedi: http://www.hp9825.com/html/hybrid_microprocessor.html.

Anche: http://www.decadecounter.com/vta/articleview.php?item=428.

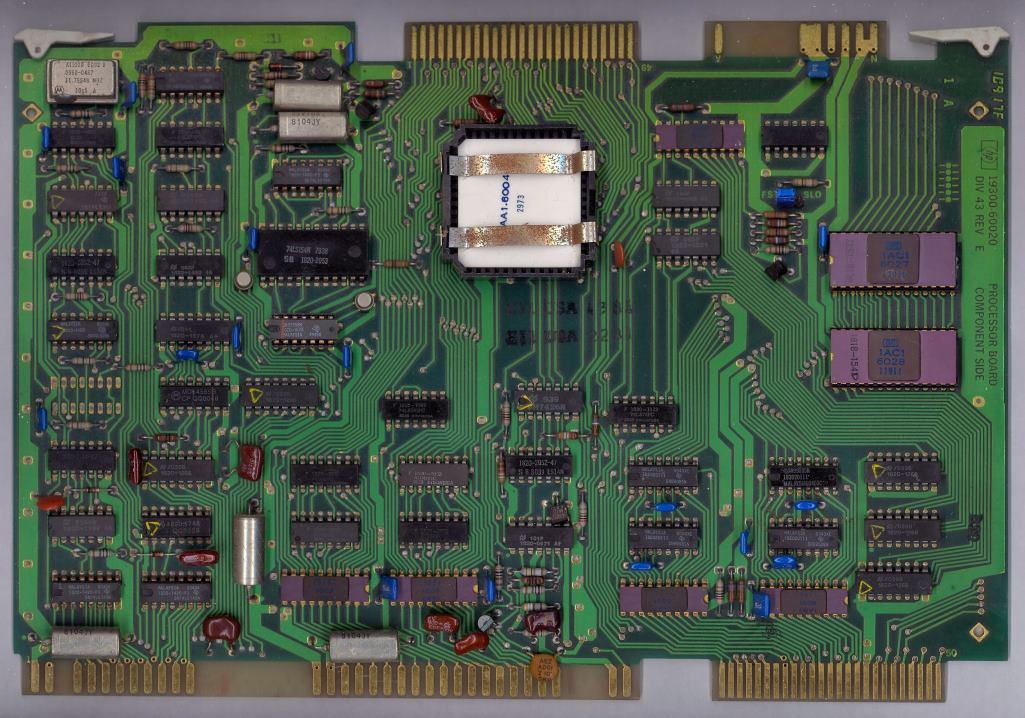

Scheda CPU del calcolatore HP 9845 con CPU HP BPC (a sinistra, col dissipatore di calore).

Vedi: http://www.hp9845.net/9845/hardware/processors/.

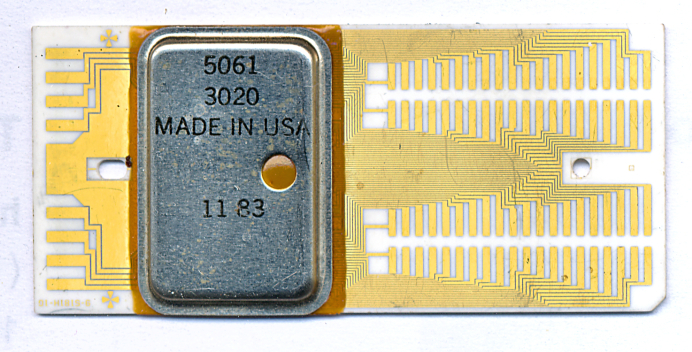

L'HP 5061-3020 (1981, questo è del 1983) era una versione "ridotta" del microprocessore BPC.

Vedi: http://www.hp9825.com/html/hybrid_microprocessor.html; http://www.decadecounter.com/vta/articleview.php?item=429.

Durante la progettazione del calcolatore 9845 HP sviluppò un microcontroller single chip dedicato alla gestione dell’unità a nastri chiamato TACO (TApe COntroller - C5061), realizzato con processo NMOS-III. TACO è stato tra i primi microprocessori e probabilmente il primo in assoluto ad essere fabbricato impiegando questo procedimento allora nuovissimo, adottato poi da molti altri produttori (vedi DEC, Intel e Motorola).

Questa scheda (controller di hard disk) per minicomputer HP 2100-A700 (1982) contiene due integrati HP NMOS in package ceramico simile a quello mostrato sopra. L'HP 2100, fino al 1975 nota come "HP 1000", era una vasta famiglia di minicomputer a 16 bit prodotti dalla metà degli anni Sessanta fino ai primi anni Novanta ed utilizzati in modo particolare come calcolatori real-time. Vedi: http://en.wikipedia.org/wiki/Hp_1000; http://www.hpmuseum.net/exhibit.php?class=3&cat=33.

CPU HP a 8 bit (identificato dalla sigla 1AE8-6001) utilizzata in uno strumento di misura 3779C (Primary Multiplexer Analyzer), 1980. Assieme al processore ci sono 4 Kbyte di ROM ed altrettanti di DRAM (due memorie Mostek 4116). Questo processore, da non confondersi col BPC della stessa HP (vedi sopra), funziona a 1,70 MHz ed è realizzato con tecnologia SOS (Silicon On Sapphire).

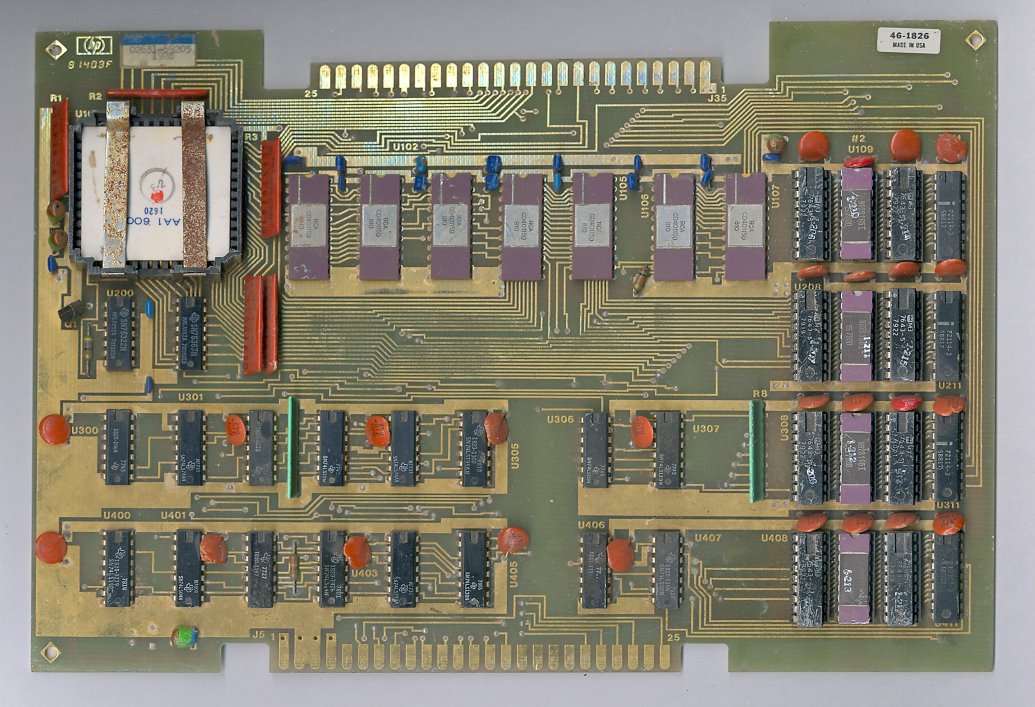

Scheda HP con CPU a 8 bit siglata 1AA1-6004 (1978).

Scheda HP con chip 1AA1-6001 (LCC a 48 pin), 1979. E' probabile che si tratti di una CPU CMOS a 8 bit, dall'architettura simile a quella nell'immagine precedente. Vi sono anche 7 convertitori di livello CMOS/TTL ad alta velocità RCA CD40115D (vedi datasheet), 4 SRAM Intel P2114-3 (1 kbit x 4) ed altrettante PROM bipolari Signetics N82S185 da 8 kbit ciascuna. La scheda è genericamente definita "Control Card".

Vedi: http://www.cpu-world.com/forum/viewtopic.php?t=10858&postdays=0&postorder=asc&start=0.

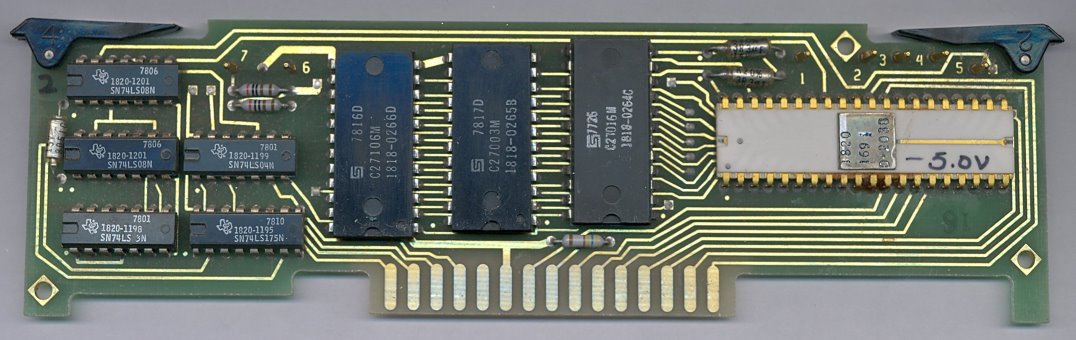

Piccola scheda HP con CPU "Nanoprocessor" (HP 1820-1691/2). Si tratta di un semplice microprocessore sviluppato in proprio da HP ed impiegato principalmente come controller nelle interfacce HP-IB (o GPIB, o IEEE-488). Il Nanoprocessor venne progettato all'inizio degli anni Settanta dalla divisione HP R&D (Ricerca e Sviluppo) di Loveland, dove veniva anche fabbricato con processo NMOS a singolo livello di metallizzazione (NMOS-I). Si trattava in realtà, vista la sua estrema semplicità, più di sequenziatore di microcodice, con affiancata un'ALU elementare, che di un microprocessore vero e proprio. Necessitava infatti di ROM di microprogramma esterne (visibili qui sopra alla sua sinistra) ed aveva un set di istruzioni molto limitato. Venne inizialmente utilizzato nella realizzazione della scheda di I/O HP-IB (HP 98034A) per il calcolatore HP 9825; in seguito trovò impiego anche in altri controller di questo tipo, ad esempio la scheda di I/O parallelo HP 98032A e la Real Time Clock Interface 98035. Il Nanoprocessor è anche utilizzato come controller della stampante termica del calcolatore HP 9845. L'unità aritmetico-logica del Nanoprocessor poteva eseguire solamente operazioni logiche e ben poco altro (confronti, salti, shift, mascheratura, chiamata di subroutine): non era dunque una ALU vera e propria, dal momento che mancava delle funzioni aritmetiche, che era necessario implementare nel microcodice oppure facendo ricorso a componenti esterni; ciò rendeva la programmazione particolarmente lenta e laboriosa. Il Nanoprocessor era inoltre caratterizzato dalla particolarità di avere una tensione di bias la cui esatta specifica poteva variare sensibilmente, tra -2 e -5 V, in "passi" di 0,5 V. Dal momento che il processo di fabbricazione scelto da HP forniva chip con diverse tolleranze, era necessaria la prova di ogni singola unità prodotta per determinarne con precisione l'appropriata tensione di bias. Ciascun processore veniva quindi marcato a mano con l'esatto valore di tale tensione (in questo caso, -5,0 V), cui corrispondeva poi l'opportuno valore di una resistenza di controllo posta sulla scheda. A causa delle molte limitazioni, l'uso del Nanoprocessor rimase confinato a poche schede di I/O; anche in questo campo esso venne in seguito rimpiazzato da più potenti microprocessori di uso generale (ad esempio l'Intel 8085). Il Nanoprocessor esiste sia nella versione con package ceramico bianco visibile qui che in quella con package ceramico "classico" (grigio: vedi questo link). Le sigle HP che lo identificano sono: 1820-1691 e 1820-1692 (vedi). La "versione" -1692 si trova principalmente nelle schede sviluppate per l'HP 9845.

Vedi: http://www.bitsavers.org/pdf/hp/98xx/98034-90000_hpibIntf_May79.pdf.

Anche: http://www.hp9825.com/html/hpib1.html.

Anche: http://www.hp9845.net/9845/hardware/processors/; http://www.classiccmp.org/pipermail/cctalk/2001-August/233006.html.

Processore HP FOCUS (1982) sulla scheda CPU di un calcolatore HP Series 3000/500 (vista frontale). FOCUS è considerata da molti la prima CPU commerciale single-chip a 32 bit. Sulla scheda visibile qui sopra trovano posto la CPU vera e propria, che funziona a 20 MHz, il processore di I/O (IOP), l'unità di gestione della memoria (MMU) e 16 KB di RAM. I chip sono realizzati con processo NMOS-III; nella fabbricazione della scheda è impiegata una particolare tecnologia a suo tempo brevettata da HP che consente la connessione dei chip direttamente alla scheda stessa (chip-on-board). Ciascun integrato è dotato di un proprio dissipatore di calore. HP rinunciò al processo SOS (Silicon On Sapphire) già impiegato in altre sue CPU per passare al più denso NMOS; ciò diede tuttavia luogo a problemi di dissipazione del calore, che i chip NMOS producevano in quantità maggiore dei SOS a parità di frequenza operativa. Per tale motivo la scheda della CPU e quella della RAM di sistema sono fabbricate in modo particolare, con una lamina di rame interposta tra due circuiti stampati (questo tipo di assemblaggio è noto col nome "finstrate"), in modo abbastanza simile a quanto fatto anni prima nel supercalcolatore Cray 1.

Vedi: http://en.wikipedia.org/wiki/HP_FOCUS; http://www.openpa.net/systems/hp-9000_520.html.

Vista del retro della scheda (HP 5061-6803). I rettangoli di plastica nera proteggono i punti di connessione dei chip al circuito stampato.

Prima motherboard PC - First IBM PC motherboard

9) Scheda madre dell’IBM PC 5150 (1981 - la scheda raffigurata qui è del 1982) - Presentato il 12 Agosto 1981 e sviluppato dall’IBM Entry Systems Division di Boca Raton, in Florida, sotto la supervisione di Don Estridge, il Personal Computer 5150 è l’antenato di tutti i moderni PC nonché uno dei prodotti di maggiore impatto tecnologico e sociale nella storia dell’informatica (vedi). Si tratta di una macchina modestissima se valutata secondo i canoni contemporanei: la CPU è un Intel 8088 (la scelta di questo processore ha fatto la fortuna di Intel e dell’architettura x86) a 4,77 MHz; la RAM di base è di soli 64 KB, espandibili a 256 (successivamente a 640); l’architettura di sistema è interamente ad 8 bit (benché l’8088 sia internamente un processore a 16 bit). Il disco rigido, costosissimo, era soltanto un’opzione riservata a pochi fortunati; gli altri si "accontentavano" di uno o due floppy da 5,25 pollici ed eventualmente di un lettore a cassette. Nella ROM di base, corrispondente agli attuali BIOS, era installata una versione del BASIC di Microsoft (altra azienda che deve gran parte della sua fortuna a questa macchina). A dispetto del costo elevato e della dotazione hardware inferiore a quella di molte macchine concorrenti, il fatto che il 5150 fosse un prodotto IBM attrasse molti utenti "professionali" per i quali questo marchio era sinonimo di affidabilità e qualità. Il successo del PC originale non fu tuttavia immediato: al momento della presentazione esistevano sul mercato numerosi altri sistemi basati su 8086/8088, in gran parte macchine CP/M; inoltre, il 5150 era lento e macchinoso nell’utilizzo delle risorse hardware, tanto che svariati programmatori preferivano bypassare il BIOS della macchina e controllare direttamente le periferiche. La chiave del successo del PC IBM fu la disponibilità di programmi di qualità, tra cui il foglio di calcolo Lotus 1-2-3, che si rivelò decisiva nel battere la concorrenza; in più, quando le vendite del 5150 cominciarono a decollare, il fatto che la sua architettura di sistema fosse ben nota e facilmente riproducibile diede il via al fenomeno dei "cloni" o personal computer "IBM compatibili", i quali in poco tempo fecero piazza pulita di quasi tutti i sistemi alternativi, in particolare di quelli CP/M che scomparvero dalla scena. Vedi anche: http://www.vintage-computer.com/ibm_pc.shtml.

Vedi: http://encyclopedia2.thefreedictionary.com/Systemboard.

Primo sistema IBM con floppy disk a lettura/scrittura - First IBM business system with read/write floppy disk (8'')

10) CPU del sistema IBM 3740 Data Entry System o DES (1973/4) - Sviluppato dagli stabilimenti IBM di Rochester (Minnesota, USA, vedi) e presentato il 22 Febbraio 1973, il DES era in sostanza una stazione di lavoro che poteva connettersi a calcolatori (mainframe) centralizzati, fungendo da terminale per l’immissione remota di dati (donde il nome). Questa macchina, grande come una scrivania, è stata il primo sistema IBM ad utilizzare dischi floppy (da otto pollici, introdotti da IBM nel 1971) R/W, cioè sia in lettura che in scrittura, nonché la prima apparecchiatura informatica IBM realizzata con circuiti integrati MOSFET a media/larga scala di integrazione. Nonostante le prestazioni fossero tutt’altro che esaltanti, il DES ebbe un buon successo commerciale, tanto che fu ritirato dal mercato solamente nel 1983. La scheda che vediamo qui è stata prodotta all’inizio del 1974. Notare i caratteristici package DIP ceramici "col buco" tipici dei primi anni Settanta. Il motivo d’interesse di questa scheda risiede proprio nel fatto che si tratta di una delle più vecchie CPU realizzate con circuiti integrati LSI nonché una delle prime applicazioni commerciali di circuiti logici programmabili (gate array) MOS: vedi http://it.wikipedia.org/wiki/Programmable_logic_device. Inoltre, è facile notare come tutta la quantità di componenti in essa contenuti potrebbe essere rimpiazzata da un singolo microprocessore. Le memorie RAM sono, probabilmente, i circuiti integrati nei contenitori quadrati di alluminio (tipo IBM MST). Vedi: http://www.corestore.org/3.htm.

Lo sviluppo del floppy disk cominciò in IBM nel 1967. All'epoca si stava cercando un sistema rapido ed affidabile (e più economico dei nastri) per effettuare il caricamento del microcodice nei mainframe System/370. Queste macchine erano infatti le prime fabbricate da IBM col microcodice contenuto in una memoria volatile anziché in una ROM permamente. Alan Shugart e il suo team crearono dapprima un "memory disk" flessibile a sola lettura con una capacità di 80 KB. Venne in seguito aggiunto il caratteristico contenitore protettivo di plastica nera e nel 1971 il floppy disk venne commercializzato da IBM insieme al suo lettore, chiamato "Minnow" (IBM 23FD) ed adoperato inizialmente nei calcolatori System/370 ed in altre macchine IBM come lo Storage Control Unit 2385. In questo primo periodo il floppy disk veniva utilizzato unicamente come mezzo per caricare programmi in memoria, dunque in sola lettura. Il primo floppy disk a lettura/scrittura fu nel 1972 il Memorex 650 (175 KB di capacità), sviluppato anch'esso da Shugart (che nel frattempo aveva lasciato l'IBM). IBM rispose nel 1973 col suo proprio floppy R/W impiegato nel Data Entry System 3740 con una capacità di 250 KB. Il suo formato divenne uno standard di fatto, conosciuto con la sigla SSSD (Single Side Single Density). Le prime unità a doppia faccia (Double Sided) furono introdotte nel 1975 da Burroughs (1 MB di capacità) e nel 1976 da IBM (500 KB, Double Side Single Density o DSSD). Nel 1977 infine furono commercializzati i primi floppy da 8 pollici DSDD (Double Side, Double Density) con 1,2 MB di capacità.

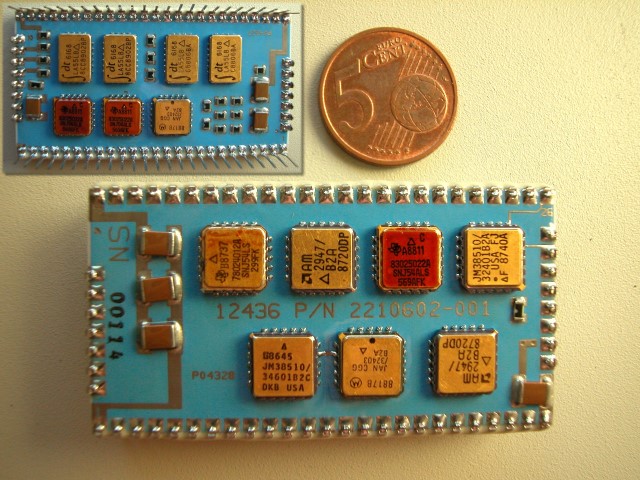

CPU di un communication processor per mainframe Amdahl/Fujitsu (1990) realizzata interamente con gate array VLSI. Si tratta di una tecnologia alternativa all’impiego di microprocessori (componenti di uso generico) basata sulla creazione di circuiti integrati dedicati ad uno specifico compito (ASIC) oppure sulla personalizzazione di gate array CMOS come ad esempio questi Fujitsu da 6.000 e rispettivamente 10.000 porte logiche ciascuno. Consente di ottenere CPU ottimizzate per particolari impieghi le cui prestazioni possono essere accuratamente valutate e regolate in fase di progettazione della macchina.

CPU Amdahl (1989) realizzata con gate array VLSI ECL (Emitter Coupled Logic) da 6.000 gate ciascuno. Le dimensioni della scheda sono circa 50 x 30 cm.

11) Scheda di calcolatore Viatron System 21 (1972 circa, vedi) - Da un’azienda che ha fatto (tanta) fortuna, IBM, ad un’altra che invece ne ha avuta ben poca: Viatron (da non confondersi con l’omonima società americana fondata nel 1990, che sviluppa programmi per l’automazione d’ufficio). Qui sopra è raffigurata una delle schede costituenti la CPU (a 16 bit) di uno dei pochi sistemi da essa prodotti prima del fallimento a causa di problemi finanziari, e precisamente il System 21 (primissimi anni Settanta). Come l’IBM 3740, era anch’esso realizzato con circuiti integrati LSI ed è stato in particolare tra i primi sistemi da scrivania a fare uso di questa tecnologia. Notare i particolari package (contenitori) dei circuiti integrati: all’epoca non s’erano ancora affermati standard "maturi" nel mondo dell’LSI ed ogni produttore tendeva ad impiegare soluzioni proprie. L’intera CPU era composta da sedici schede, di cui otto riservate al "microprocessor" o processore vero e proprio (all’epoca questo termine veniva talvolta impiegato per indicare le CPU realizzate con circuiti LSI, mentre oggi con esso s’intende un processore realizzato in un unico circuito LSI/VLSI, o "monolitico"). Il System 21 possedeva anche, cosa questa decisamente avanzata per l’epoca, una memoria RAM realizzata unicamente con circuiti integrati – erano quelli gli anni, ricordiamolo, delle memorie a nuclei magnetici.

Gli anni Settanta hanno visto il rapido sviluppo delle tecnologie LSI/VLSI grazie alle quali è stato possibile integrare dapprima migliaia e poi milioni di transistor in un singolo circuito integrato. Ciò ha reso possibile la realizzazione di apparecchiature sempre più piccole e potenti (ad es. in termini di velocità di calcolo e di capacità di memoria). Qui si vede un gruppo di array MOS LSI sulla scheda di una calcolatrice elettronica Sanyo ICC-081 (1971, vedi: http://www.vintagecalculators.com/html/sanyo_icc-0081_mini_calculator.html). I circuiti integrati sono fabbricati da General Instruments. Pur contenendo solamente poche centinaia di transistor circuiti come questi rappresentavano all’epoca un enorme passo in avanti rispetto alle tecnologie esistenti e costituirono la base sulla quale si sviluppò l’industria dei microprocessori.

Logica di controllo di un terminale NCR M15 (circa 1975) realizzata con circuiti LSI AMi. La scheda a sinistra contiene la memoria RAM/ROM (in basso a sinistra un dettaglio), quella a destra la CPU. All’inizio degli anni Settanta questo tipo di processori era spesso chiamato "micro-processor" così come i microprocessori single-chip veri e propri, intendendo con tale termine una CPU interamente realizzata con circuiti integrati LSI.

Altro esempio di "micro-processor" implementato con LSI MOS (circa 1974): la logica di controllo di un terminale CENDAC.

12) Modulo TCM della CPU di un sistema IBM S/390 9021 (1991) - Che cosa distingue un normale PC da un costosissimo mainframe, cioè un grande calcolatore? La potenza di calcolo, la capacità di memoria, il numero di periferiche, il fatto di essere un sistema e via elencando: tutto giusto. Bisogna fare però anche una considerazione tecnologica: in questo tipo di calcolatori vengono applicate soluzioni hardware all’avanguardia, in termini sia di prestazioni che (soprattutto) di affidabilità. A causa del costo elevato esse non potrebbero mai venir "importate" nel mondo PC al momento della loro nascita, ma che con l’andare del tempo giungono anche nei sistemi di fascia media e bassa. Qui sopra si vede il retro di uno dei moduli multichip TCM che costituiscono la CPU di un IBM S/390 (1991). Quelli che sembrano "puntini" di forma circolare sono in realtà i pin di collegamento di altrettanti contatti per i segnali e l’alimentazione elettrica. Un "TCM" (Thermal Conductivity Module, "modulo a conduzione termica" è in sostanza un substrato di ceramica sul quale sono collocati i chip VLSI costituenti la CPU del sistema, assieme ad una gran quantità di connessioni, racchiuso in un contenitore di alluminio che ha lo scopo di trasmettere il più efficacemente possibile il calore prodotto durante il funzionamento al sistema di raffreddamento, che può essere ad aria oppure a liquido (come in questo caso). All’interno del TCM (il cui brevetto ha fruttato ad IBM diversi premi per l’innovazione tecnologica) un olio speciale assicura la ripartizione uniforme del calore e la sua efficiente dispersione. Molti articoli sui TCM (vedi), con schemi dettagliati ed informazioni tecniche, si trovano in questo sito web di IBM: http://www.research.ibm.com/journal/rd.

Vedi: http://www.research.ibm.com/journal/rd/353/ibmrd3503C.pdf; http://www.research.ibm.com/journal/rd/365/ibmrd3605C.pdf.

Vedi: http://ibmcollectables.com/gallery/view_album.php?set_albumName=album122.

Anche: http://www.research.ibm.com/journal/rd/365/ibmrd3605I.pdf; http://www.thegalleryofoldiron.com/TCMS.HTM.

Il sistema Parallel Enterprise Server S/390-G3 9672 (1997) segna il passaggio di IBM nella fascia dei mainframe dalla tecnologia bipolare impiegata nelle precedenti versioni del 390 alla CMOS, con notevoli guadagni in fatto di potenza richiesta, di numero di transistor (e dunque di funzioni) integrabili in un chip e di dimensioni della CPU (vedi: http://www.research.ibm.com/journal/rd/414/rao.pdf). Continuano ad essere utilizzati moduli multichip (MCM) ma questi ultimi sono ora molto più "densi", nel senso che contengono più funzioni rispetto a prima. L’MCM raffigurato nell’immagine 11 contiene ad esempio circa 100 circuiti integrati bipolari LSI; quello raffigurato qui sopra (il componente più grande al centro della foto) ne ospita solo 34, ma vista la scala di integrazione molto maggiore il risultato è equivalente a quello che si otterrebbe con 50 MCM del primo tipo. In questo modo si ottiene una riduzione del consumo di energia del 97% circa e del 93% dello spazio occupato.

Vista di dettaglio laterale di un MCM dell’IBM S/390-G3 9672 (si riferisce alla medesima scheda raffigurata più sopra).

Vedi: http://www.research.ibm.com/journal/rd/414/rao.pdf; http://www.hindawi.com/getarticle.aspx?doi=10.1155/apec.10.31.

Vedi: http://www.research.ibm.com/journal/rd/425/perfecto.html; http://www.jhuapl.edu/techdigest/td2001/Blum.pdf.

13) Scheda della CPU di un sistema IBM 4341 (1982, vedi) - L’IBM ha profuso molti sforzi nel campo del packaging, parola con la quale si intendono le tecnologie di incapsulamento dei componenti elettronici e degli altri elementi che costituiscono i calcolatori; in questo settore ha infatti introdotto molte innovazioni entrate poi nell’uso comune. Fin dagli anni Cinquanta "Big Blue" ha adottato una strategia di razionalizzazione e standardizzazione delle parti dei propri computer, con lo scopo di migliorarne l’efficienza e di semplificarne nello stesso tempo la manutenzione. Fra le altre cose IBM è stata tra i primi fabbricanti di hardware ad utilizzare nei propri prodotti commerciali moduli multichip (che cioè racchiudono più circuiti integrati in uno stesso contenitore). Quando questa tecnologia è stata impiegata nei calcolatori della serie 4300, all’inizio degli anni Ottanta, essa rappresentava una soluzione assolutamente all’avanguardia. Il principale vantaggio dei multichip in anni in cui il numero dei componenti che si potevano integrare in un singolo circuito VLSI era molto più basso di oggi risiede nel fatto che permettono di ottenere schede molto "dense", risparmiando spazio e lunghezza delle connessioni nei circuiti stampati (elemento chiave nel determinare la velocità di un calcolatore).

Vedi: http://www.research.ibm.com/journal/rd/271/ibmrd2701D.pdf; http://www.research.ibm.com/journal/rd/263/ibmrd2603C.pdf.

Sulle tecnologie di packaging IBM: http://www.research.ibm.com/journal/rd/255/ibmrd2505X.pdf.

14) Scheda del calcolatore Cray X-MP (1982, vedi) - Ci sono nomi che non hanno bisogno di presentazione: nel mondo dell’informatica, Cray è uno di questi. Benché questa compagnia (la cui attuale denominazione è Cray Inc.) stia oggi attraversando un periodo di difficoltà finanziarie, il suo marchio rimane legato a doppio filo ad una leggendaria tradizione. Una macchina Cray, infatti, è "il" supercomputer per antonomasia – e tale rimane anche se esistono calcolatori più potenti e più veloci. Qui vediamo una delle schede che compongono la CPU di un Cray X – MP (1982), macchina progettata da Steve Chen quale successore del primo calcolatore Cray, il Cray – 1 (1976). L’X – MP è stato il primo supercalcolatore vettoriale ad avere un buon successo commerciale, nonché (tra il 1983 ed il 1985) il più veloce computer al mondo, con una potenza di 230 MFLOPS (circa 450 nella versione a due processori). La CPU funzionava a 112 MHz, frequenza elevatissima per l’epoca, con un ciclo di 8,5 microsecondi. Come tutti i primi calcolatori Cray, anche l’X – MP era realizzato con circuiti integrati semplici ma veloci, di tipo ECL (all’epoca era questa la tecnologia che permetteva le frequenze di lavoro più alte). Tali circuiti erano montati in schede a cinque strati (come quella in figura) con "anima" in rame laminato, ciascuna delle quali poteva contenerne fino a 144. Il tutto era a sua volta collocato in speciali rack (armadi), il cui design era volto ad ottenere le massime prestazioni abbreviando quanto più possibile la lunghezza delle interconnessioni elettriche. La lamina in rame inserita in ciascuna coppia di schede serviva a trasferire il calore dalle schede medesime a degli appositi "collettori" collocati alle estremità dei rack, da dove veniva asportato tramite un meccanismo di raffreddamento a freon (che diede inizialmente non pochi problemi di affidabilità). Gli X – MP erano macchine a 64 bit, con 128 MB di RAM; nel 1984 costavano circa 15 milioni di Dollari (più il costo dei dischi). Per avere un’idea di quanto sia progredita nel frattempo la tecnologia dei microprocessori, basti pensare che un attuale Intel Core Duo E6700, che può essere montato in un normale PC desktop, è capace di circa 12,53 GFLOPS: la potenza di calcolo dell’X – MP non è che l’otto per cento di questo valore. Tra gli acquirenti dei primi sistemi Cray figurano agenzie ed enti governativi americani (NASA, NSA, Dipartimento della Difesa ecc.), università e centri di ricerca, specialmente nel campo della fisica atomica. Queste macchine hanno avuto l’enorme merito di aprire il campo del supercalcolo vettoriale e parallelo ad una quantità di soggetti che, pur disponendo di mezzi economici consistenti, non avrebbero trovato economico l’acquisto dei supercalcolatori esistenti all’epoca (es. il CDC 7600, o l’ILLIAC IV). I Cray, infatti, avevano un miglior rapporto prezzo/prestazioni ed un’affidabilità di gran lunga superiore. I successori diretti dell’X – MP furono il Cray 2 (1985, 500 – 713 MFLOPS) e l’Y – MP (1987), realizzato con tecnologie VLSI.

Scheda di un Cray 1 S/1000 (1979, l'esemplare è del 1981). La serie "S" è un'evoluzione del Cray 1 originario, con un ciclo più rapido (12 ns contro 12,5 ns corrispondenti ad 80 MHz). L'S/1000 in particolare ha una memoria RAM con una capacità di 1 Mword (a 64 bit, corrispondenti a 8 MB). Il Cray 1 è stato il primo supercalcolatore commerciale basato su circuiti integrati (ECL a bassa densità di integrazione). Una macchina completa contiene circa 230.000 gate logici (tanti quanti ne ha l'Intel 386), "ripartiti" tra soli 4 tipi diversi di integrati fabbricati da Fujitsu. I registri sono contenuti in SRAM ad alta velocità (6 ns) 16x1, mentre per la RAM principale vengono impiegate SRAM 1.024x1, 50 ns. Ciascuna scheda contiene un massimo di 144 integrati; la macchina intera ha in tutto 1.662 schede di 113 tipi diversi. I Cray 1 S hanno una velocità di calcolo di circa 80 MIPS; in queste macchine il sottosistema di I/O è contenuto in un armadio separato rispetto a quello della CPU, ed è collegato ad esso tramite un canale di controllo (6 MB/s) ed un canale dati ad alta velocità (100 MB/s). La logica del Cray 1 è stata progettata e realizzata minimizzando il numero di tipi di integrati ECL utilizzati: il 95% di essi sono doppie porte NAND 5/4 (cinque/quattro ingressi), in logica negativa, con output complementari. Il ritardo di propagazione è di 750 ps, a fronte di un assorbimento di 60 mW per porta (120 mW per chip).

Vedi: http://american.cs.ucdavis.edu/academic/readings/papers/CRAY-technology.pdf.

Vedi: http://www.craywiki.co.uk/index.php?title=Cray_1S.

Vedi: http://archive.computerhistory.org/resources/text/Cray/Cray.CRAY1S.1979.102646188.pdf.

Scheda processore di un calcolatore parallelo MasPar MP-2 (1992). La MasPar Computer Corp., fondata nel 1987 da J. Kalb (che era stato vicepresidente della divisione VLSI di DEC), è stata per qualche anno, fino alla sua liquidazione nel 1996, un fabbricante di calcolatori paralleli ed in particolare di macchine SIMD (MP-1 ed MP-2) con architettura di tipo Harvard. Ciascuna "node-board" o scheda-processore contiene 32 chip, ognuno dei quali integra a sua volta 32 ALU (unità logico-aritmetiche) a 32 bit, realizzate con integrati CMOS full-custom fabbricati da HP o Texas Instruments (processo a 1 micron, doppia metallizzazione, 80 ns) e suddivise in due blocchi da 16 ognuno dei quali fa capo un'interfaccia di memoria comune (detta "M-machine"). L'intera scheda contiene dunque 1K (1.024) ALU. Ciascun chip, chiamato "PE-slice" e dotato di 512 KB di memoria RAM locale, è interconnesso con altri 8; a loro volta, le node-board sono collegate tramite uno switch centralizzato (l'intero sistema può avere al massimo 16K = 16.384 unità di elaborazione). I calcolatori MasPar, contrariamente alla maggior parte dei supercomputer dell'epoca, non erano macchine vettoriali bensì SIMD (Single Instruction Multiple Data). Queste macchine, prodotte in volumi ridotti (non più di 250 MP-2 in totale) sono state impiegate prevalentemente in applicazioni di calcolo scientifico e di elaborazione di immagini, ad esempio dalla NASA. La maggior parte degli MP-1 e -2, che come sistema operativo utilizzavano una versione ad hoc di Unix, sono stati venduti nella versione con 4K (4.096) "processori" (vedi ad esempio questo collegamento, che fa riferimento ad un articolo del 1993: http://www.lbl.gov/Science-Articles/Archive/maspar-computer-installed.html, oppure anche questo documento: http://nvl.nist.gov/pub/nistpubs/jres/101/2/j2anut.pdf). Un MP-2 con 16K "processori" poteva raggiungere una potenza di calcolo di 2,4 GFLOPS a doppia precisione.

The MasPar Computer Corporation's MP-1 system, introduced in 1990, features a SIMD array of up to 16K 4-bit processors organized as a two-dimensional array with each processor connected to 8 nearest neighbors. MasPar refers to this interconnection topology as the X-Net. The MP-1 also contains an array control unit that fetches and decodes instructions, computes addresses and other scalars, and send control signals to the processor array. An MP-1 system of maximum size has a peak speed of 26 GIPS (32-bit integer operations) or 550 MFLOPS (double precision) and dissipates about 1 kilowatt. The maximum memory size is 1 GB, and the max. bandwidth to memory is 12 GB/s. When the X-Net is used, the maximum aggregate inter-PE communication bandwidth is 23 GB/s. In addition, a three-stage global routing network is provided, utilizing custom routing chips and achieving up to 1,3 GB/sec aggregate bandwidth. [...] Although the processor is internally a 4-bit device, it contains 40 programmer-visible, 32-bit registers and supports integer operands of 1, 8, 16, 32 or 64 bits. In addition, the same hardware performs 32- and 64-bit floating point operations. [...] MasPar is able to package 32 of these 4-bit processors on a single chip, illustrating the improved technology now available (2-level metal, 1,6 micron CMOS, 450.000 transistors). Each 14'' by 19'' processor board contains 1.024 processors, clocked at 80 ns, and 16 MB of ECC memory, organized as 16 KB per processor and implemented using 1 Mb DRAMs. [...] The 2nd generation MasPar, MP-2, maintains the same system architecture as the MP-1 but with the processors upgraded to 32-bit engines. MasPar is still able to fit 32 processors in one chip, and the heat load remains a relatively modest kilowatt. The VLSI technology is now two-level metal, 1 micron CMOS, and the clock is 80 ns. Peak speed is now 68 GIPS (32-bit integer operations) or 2,4 GFLOPS (double precision). (Almasi, Gottlieb, Highly Parallel Computing, Benjamin Cummings 1994, pag. 458)

Circa l'architettura del MasPar MP-1 vedi: http://www.cs.uiuc.edu/class/sp08/cs533/reading_list/14a.pdf.

Anche: http://www.ssrc.ucsc.edu/PaperArchive/elghazawi-frontiers95.pdf.

Anche: http://www.fou.uib.no/fd/1996/h/413002/node51.html; http://people.engr.ncsu.edu/efg/506/sum99/001/lec8-mp.pdf.

Sulle architetture SIMD in generale: http://www.cs.ucr.edu/~bhuyan/CS213/2004/LECTURE2a.pdf.

Anche: http://www.cs.nthu.edu.tw/~ychung/slides/para_programming/parallel.pdf.

Un esempio di applicazione: http://www.ece.umassd.edu/FACULTY/acosta/ICASSP/Icassp_1995/pdf/ic951832.pdf.

Vedi anche questo documento, oppure: http://adsabs.harvard.edu/abs/1991SPIE.1492..229F.

Anche: http://multimedia.ece.uic.edu/93-7.pdf; http://bioinformatics.oxfordjournals.org/cgi/reprint/12/4/269.pdf.

Macchine MasPar alla NASA: http://ntrs.nasa.gov/archive/nasa/casi.ntrs.nasa.gov/20020086319_2002139424.pdf.

Sulla storia della MasPar Computer Corp.: http://www.kellogg.northwestern.edu/faculty/VanMieghem/htm/mascase_Pag1.pdf.

Sulla storia del calcolo parallelo: http://ei.cs.vt.edu/~history/Parallel.html.

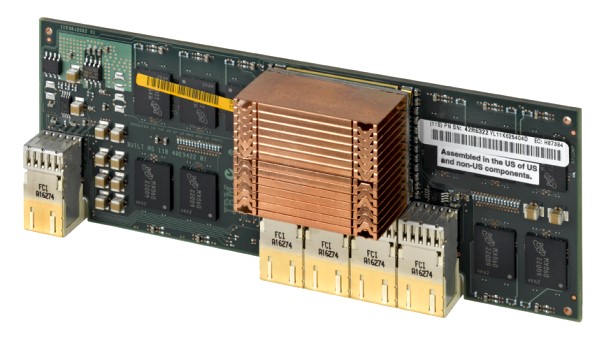

Node board di un supercomputer a parallelismo massiccio IBM BlueGene/P (2007). Contiene 32 nodi (processori) collocati su moduli (daughterboard), ciascuno dei quali integra in un unico ASIC 4 core PowerPC 450 a 850 MHz, ed ha una potenza di calcolo teorica di circa 435 GFLOPS. Il consumo medio è di 17 Watt per nodo, grazie all'elevato livello di integrazione ed al processo produttivo impiegato, CMOS a basso consumo. La scheda misura circa 50 per 60 centimetri. Nella parte centrale della scheda, dove si trova la penna, ci sono 8 moduli di I/O. Ciascun nodo ha a bordo 2 GB di RAM DDR. Il BlueGene/P, direttamente derivato dal predecessore BlueGene/L (rispetto al quale impiega processori con 4 core PPC450 anziché con 2 PPC440, funzionanti a 850 anziché a 700 MHz) è formato da più rack (fino a 216) contenenti ciascuno un massimo di 32 schede come questa, per un totale di 884.736 CPU che assicurano una potenza di calcolo teorica di circa 3 PFLOPS (3.000 TFLOPS). Qui si vede una scheda identica a questa: http://en.wikipedia.org/wiki/Blue_Gene. La famiglia di macchine BlueGene è nata dalla collaborazione tra l'IBM ed il Lawrence Livermore National Laboratory iniziata nel 2001 con lo scopo di sviluppare calcolatori a parallelismo massiccio dalla potenza di calcolo sufficiente allo studio di processi bio-molecolari complessi quali la formazione della struttura tridimensionale delle proteine, la cui simulazione richiede notevoli risorse computazionali.

Schema dei diversi livelli successivi che costituiscono il BlueGene/P, dal singolo processore/circuito ASIC con 4 core (in basso a sinistra) fino alla macchina completa (da http://www.idris.fr/eng/Resources/index-babel.html).

BlueGene/P: dal chip al supercomputer (vedi: http://www.sentilla.com/blog).

Dettaglio di due nodi, ciascuno con un processore contenente 4 core PPC450 e 2 GB di RAM DDR. Ogni nodo ha una potenza di calcolo di circa 13,6 GFLOPS (a 850 MHz).

Vista frontale di un nodo (computing node), identico a quelli visibili nella foto sopra (immagine tratta dal sito IBM).

Sull'architettura del BlueGene/P: http://www.scc.acad.bg/documentation/team.pdf.

Anche: http://www.nsc.liu.se/lcsc2007/presentations/LCSC_2007-tengwall.pdf.

Anche (sito IBM): http://www.research.ibm.com/journal/rd49-23.html.

Un calcolatore BlueGene/P completo: http://www.flickr.com/photos/argonne/3334947628/in/set-72157614641754153/.

Una scheda come questa: http://www.flickr.com/photos/argonne/3366250577/in/set-72157614641754153/ (in questo set di fotografie dell'Argonne National Laboratory si vedono anche alcune applicazioni di supercalcolatori come il BlueGene).

15) Scheda CPU di un AT&T 3B15 con processore WE32200 (1986, vedi) - Storicamente il primo microprocessore tutto a 32 bit (sia internamente che a livello di bus) è stato nel 1980 il BELLMAC 32A sviluppato dai Bell Labs (divisione di AT&T), che dopo lo smembramento della stessa AT&T nel 1984 venne commercializzato col nome di WE32000 in quanto prodotto dalla Western Electric, società facente parte dell’ex gruppo AT&T. Questa CPU è stata usata nei primi "supermicro" (sistemi basati su microprocessore a 32 bit) messi in commercio, le macchine Unix della serie AT&T 3B (il desktop 3B2 ed i due server 3B5 e 3B15). Al 32000 originale seguirono due versioni migliorate ma pienamente compatibili con la prima: la 32100 (sotto, vedi) con 256 byte di cache integrata e la 32200 (sopra, vedi) funzionante ad una frequenza più elevata (22 MHz anziché 18).

Dettaglio della CPU 32200 e del memory controller 32206. Il clock (WE32102-W) ha una frequenza di 22 MHz.

Una CPU WE32100 nel caratteristico package PGA "rettangolare".

16) CPU Intergraph Clipper C4 - Rev. 3 (1992, vedi) - I processori a 32 bit Clipper, sviluppati dalla Fairchild in collaborazione col produttore di workstation grafiche Intergraph (l'architettura divenne proprietà della stessa Intergraph nel 1987) sono uno dei primi esempi commerciali di architettura RISC avanzata. Alcune soluzioni hardware adottate al loro interno, specialmente nella versione più recente e potente, la C4 (o C400), sono state poi riprese in altre CPU di maggior successo. Un esempio è la "traduzione", effettuata internamente al processore, delle istruzioni complesse in gruppi di istruzioni elementari - un’idea poi impiegata ad esempio negli AMD K6 e K7 per tradurre le istruzioni del codice macchina x86 (CISC) in istruzioni elementari RISC86 eseguite dalle varie unità funzionali della CPU. Il C4 è composto da tre circuiti integrati principali (CPU, FPU e MMU o unità di gestione della memoria) ai quali si aggiungono uno o due chip di memoria cache, successivamente integrati assieme alla MMU in un unico componente (CAMMU, vedi sotto). Il processore Clipper è stato utilizzato in alcune workstation Intergraph di fascia alta, equipaggiate con una specifica versione di Unix (CLIX), ed in pochi altri sistemi (fabbricati da High Level Hardware ed Opus).

Scheda Opus Systems 300PM con CPU Fairchild Clipper C3 a 33 MHz (1988). Presentata nel 1987, questa scheda add-on per PC AT è stata la capostipite della serie Opus Personal Mainframe (PM). Consentiva in sostanza di trasformare un ordinario PC x86 (80286 o 80386) in un server multiutente capace di eseguire il medesimo sistema operativo di classe Unix e gli stessi programmi sviluppati per l'architettura Clipper. Il PC di base veniva utilizzato per le operazioni di I/O (dischi, rete eccetera). Un annuncio dell'introduzione di questa scheda è visibile in questa pagina (da InfoWorld). Il Clipper C300 è il predecessore del più potente C400 (o semplicemente C4) raffigurato sopra. Vedi: http://www.decodesystems.com/help-wanted/index.html#opus.

CPU Clipper C400 (C4), (1990, questo esemplare è del Novembre 1993), in una workstation Intergraph Series 2700. I componenti che formano il processore sono riuniti in una scheda (daughterboard) connessa alla scheda madre mediante un bus dedicato a 32 bit. Vi sono tre integrati PGA: CPU, FPU e MMU, identificata in questo caso dalla sigla "CAMMU" (acronimo di Cache And Memory Management Unit). Quest'ultima contiene la cache (nelle versioni più recenti), i TLB e la logica di gestione della memoria virtuale e della protezione della memoria. La CPU è formata da 160.000 transistor ed è contenuta in un package ceramico PGA a 299 piedini, identico a quello della FPU. All'inizio degli anni Novanta il Clipper C4 era l'unica CPU RISC sia superscalare (poteva dunque eseguire più di un'istruzione contemporaneamente) che "super-pipelined". Nella workstation Intergraph 2700 il C400 funziona a 33 MHz. La microarchitettura del Clipper si discosta dal tradizionale approccio RISC in quanto dispone una serie di istruzioni complesse (pensate per aumentare la densità del codice) implementate in un'apposita memoria ROM contenuta nella CPU e detta "Macro Instruction ROM". In questo esemplare del 1993 la MMU e la cache da 128 KB (64 I + 64 D) sono integrate nell'unico chip CAMMU; nella precedente revisione (vedi immagine 16) del processore C400 esse sono invece implementate come componenti separati. L'Intergraph 2700 era una macchina indubbiamente avanzata per l'epoca in cui venne presentata (fine 1992): pur essendo infatti progettata come workstation desktop di medio livello, poteva avere fino a 256 MB di RAM e schede grafiche accelerate per CAD e progettazione assistita.

Vedi: http://www.eecs.berkeley.edu/Pubs/TechRpts/1987/CSD-87-329.pdf; http://en.wikipedia.org/wiki/Clipper_architecture.

Una CPU identica è visibile qui.

Prima implementazione dell’architettura SPARC - First implementation of the SPARC microarchitecture